HyperLynx update automates SerDes validation

Mentor, a Siemens business, has extended its HyperLynx PCB simulation suite to automate the manual and often resource-hungry task of SerDes channel validation.

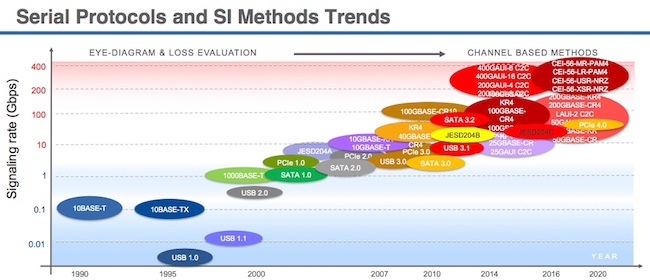

With increasing signaling rates and a proliferation in SerDes standards and specifications, board designers have become increasingly challenged when seeking to ensure compliance.

Few can hold details of all the specs in their own heads, and even after consulting printed documentation, they also typically need to draw on experts in electromagnetic simulation and signal integrity. As you would expect, ever faster speeds and performance means ever more complex compliance requirements.

Figure 1. SerDes protocols are proliferating at a faster rate than most engineers can manage (Mentor)

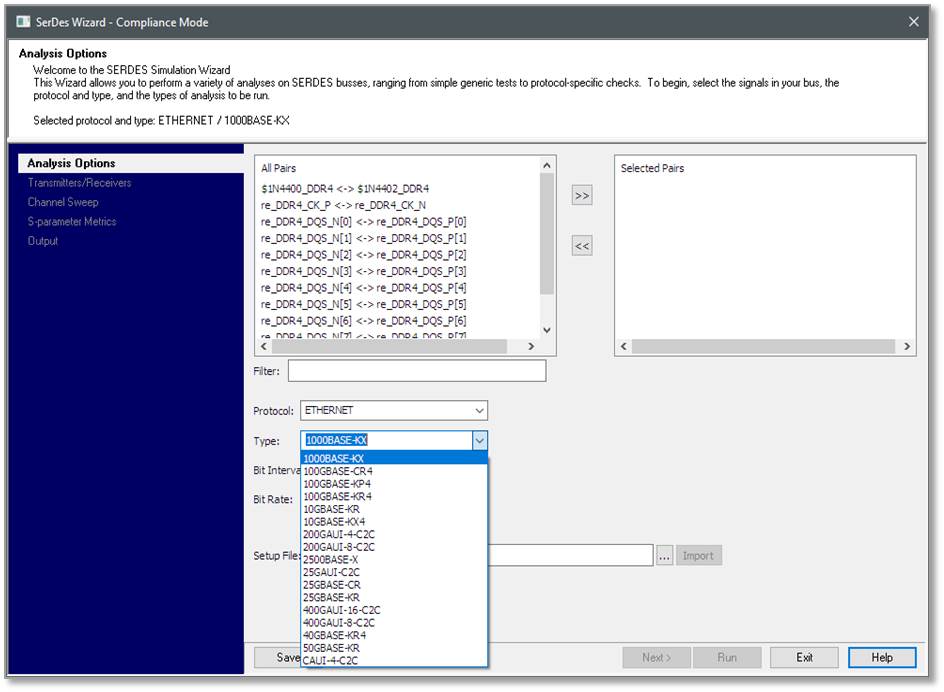

Mentor has therefore extended HyperLynx to include technology that can breakdown a channel into 2.5D and 3D components as necessary for modeling, and then run compliance checks across more than 25 SerDes protocols, including PCIe 4.0, SATA 3.2, USB 3.1 and many more.

Overall, the goal is both to speed design flows and reduce that reliance on SI and EM experts, who are themselves in short supply.

The company is committed to updating the roster of checks in its Hyperlynx SerDes Compliance Wizard as more standards emerge.

The associated HyperLynx 3D Explorer also serves to support topology exploration and optimization.

Figure 2. The HyperLynx Compliance Wizard automates validation of more than 25 SerDes protocols (Mentor)

The tool has been undergoing beta tests for some time. One trial user, Dutch design house Sintecs, used the Explorer and Wizard on development of a ‘data center in a box’ projected funded by the European Union.

It found that the automated channel extraction feature was much quicker and largely obviated its need to add a 3D full-wave solver expert to the project.

Both products will be available from the end of February 2018. Further information on the validation technology is available at the Mentor website.