How automotive test is evolving for the age of autonomous vehicles

Automotive test has long faced a high bar because of its inherent safety requirements. That has been raised higher by the move toward autonomous vehicles. These require electronic systems offering high levels of artificial intelligence and machine learning at the lowest possible latency. These ICs are becoming some of the most sophisticated and demanding designs.

A new white paper addresses automotive test technologies that can be used to achieve sufficiently comprehensive coverage in this new era across a number of key areas. These include:

- In line self-test for monitoring during functional operation.

- Defect-oriented test to reduce DPPM.

- Analog fault simulation for mixed-signal test.

Author Stephen Pateras, product marketing manager for Automotive Test at Mentor, A Siemens Business, considers each category in terms of features within the company’s Tessent tool suite. His full paper also contains a review of new techniques addressing defect tolerance and FMEDA (failure modes, effects and diagnostic analysis).

In line self-test

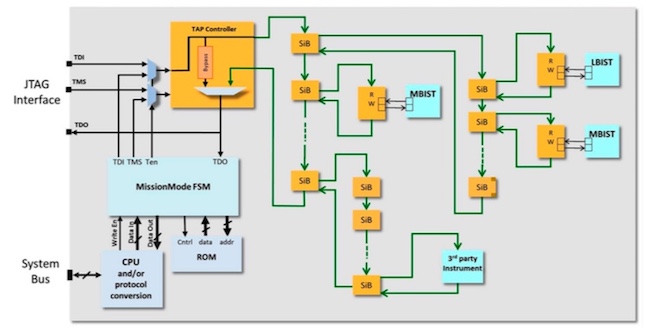

Pateras describes how Tessent uses an IJTAG-based (IEEE 1687) architecture called MissonMode to enable both system test across an entire chip – to and from a CPU bus for CAN, LIN or I2C access – and the configuration of controllers that address specific groups of test IP, down to the single block latency.

An overview of the MissionMode architecture is shown in Figure 1.

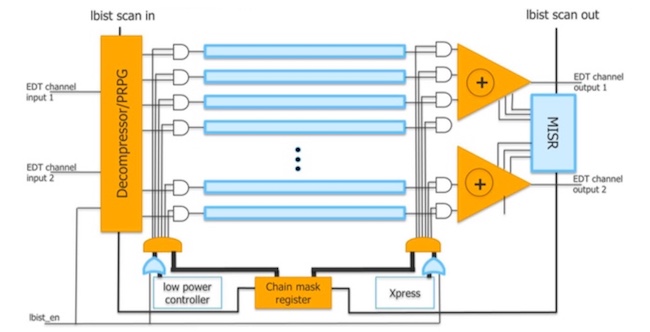

Other features include a non-destructive memory BIST feature, composed of short transaction bursts that progressively target each different memory location. There is also a reduced overhead implementation of hybrid automated test pattern generation (ATPG) with logic BIST (Figure 2).

A consistent theme throughout these automotive test strategies is that they can be implemented with minimized impact on ongoing functional performance of the system, device or block.

Reducing DPPM during automotive test

As more complex automotive devices have sought to leverage the advantages of smaller process geometries, traditional stuck-at fault models and their more complex successors have become less effective in terms of identifying defects.

“The main problem,” Pateras writes, “is that all of these existing fault models only consider faults on cell inputs and outputs and only some defects on interconnect ines between these cells. In other words, only faults abstracted to the netlist level are explicitly considered.

“It turns out, however, that increasingly more defects occur within the cell structures. For the more advanced technology nodes and associated fabrication technologies, some estimates put the number of defects found within cells to represent almost half of all circuit defects. Various types of interconnect defects are becoming prevalent as well.”

To address this, Pateras proposes a combination of two automotive test methodologies. Cell-aware test (CAT) and Layout-aware bridge extraction.

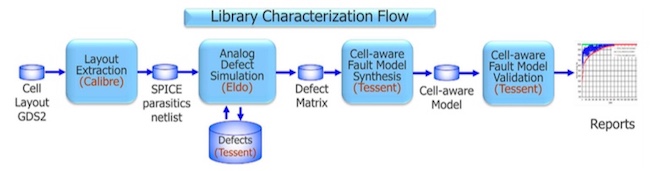

CAT focuses on shorts and opens internal to each cell. It begins with automated library characterization based on the GDSII physical layout and logic behavior associated with each cell according to their process node. This provides the information from which the input values for each fault within each cell are derived (Figure 3).

Layout-aware bridge extraction focuses on interconnects between the cells. It begins by creating a database based on the design’s LEF and DEF files, identical to that already used for layout-aware diagnosis. It enables creation of a user-defined fault model that identifies critical area bridges for analysis in ATPG.

Analog fault simulation

According to ON Semiconductor, analog faults now account for 78.6 per cent of electronic breakdowns in automotive ICs.

To some extent, this is a reflection of the faster rate at which digital test has evolved against that for AMS circuitry. However, for safety critical designs, the real issue is fault tolerance.

Analog fault simulation has, however, made significant progress in recent years, Pateras notes, with concepts from academic papers now beginning to appear in commercial tools, such as Mentor’s own Tessent DefectSim.

“[Its} basic approach is to measure the coverage of opens and shorts and related parametric variations within a transistor-level netlist,” he writes. “Coverage of a given defect is determined by evaluating a change in the circuit response in the presence of the defect through analog simulation.

“What makes this approach now practical is the use of a number of significant speed-up techniques…. [These] include such things as likelihood-weighted random sampling to ensure most time is spent simulating the most likely defects, and mixed-model simulation where the highest-level model or netlist is used for each sub-circuit instance that does not contain the defect being simulated.”

‘IC Test Solutions for the Automotive Market’ is available for immediate download.