Mentor builds simulation-emulation bridge to ‘Verification 3.0’

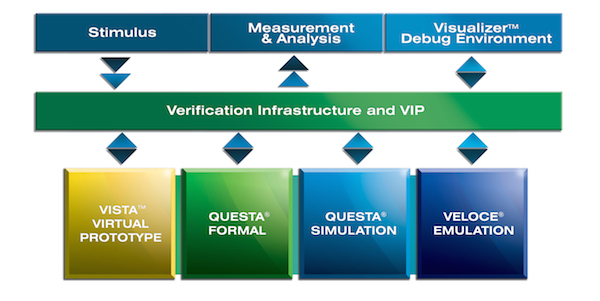

Mentor Graphics has launched the Enterprise Verification Platform (EVP) to much more tightly integrate simulation and emulation for acceleration, reuse and debug. CEO Wally Rhines unveiled the new platform as illustrating the company’s vision of ‘Verification 3.0’

EVP’s new features reflect increasing adoption of emulation, particularly once designs pass 250 million gates, and aims to make the technique easier-to-use while more explicitly exposing the ROI on what are still hefty (at least $1m+) investments.

The cornerstone is a new emulation operating system, Veloce OS3. Most significantly, it will allow a much larger number of simulation tasks to be run in emulation.

For example, Veloce boxes will now support SystemVerilog functional coverage, assertion-based verification and testbenches, UPF for low-power verification and both UVM and C/C++ testbenches.

This aspect most explicitly enables greater reuse and speeds the simulation-to-emulation port for acceleration, software test and other jobs.

A further enhancement is the introduction of a Unified Coverage Database providing coverage data in a common format for Mentor’s Questa simulation and Veloce environments. This aims to help project managers determine when to move from one to the other as well as give a more consistent view of overall progress.

The full suite then adds an integrated hardware debugger, Visualizer; an integrated software debugger, Codelink; verification IP common to both Questa and Veloce; and support for virtual peripherals to move emulators from the lab into data centers.

Emulation unbound

Moving emulation out of the lab is at the heart of Mentor’s push to justify emulation’s cost. Many new users have already bought boxes because, as John Lenyo, VP and GM for the company’s Design Verification Technology group, acknowledged, they feel they no longer have a choice: gate counts and complexity have reached that point.

EDA vendors continue to eke performance enhancements out of the code in simulation tools. But they no longer get as great a performance boost from new generations of processors since architectures shifted to multicore. Earlier and wider use of formal techniques has helped too, but the greater role of software in verification has also pushed the emulation market forward. EDA Consortium data shows the sector growing from $188m in 2010 to $363m in 2012.

Nevertheless, there are still more potential customers to convince. And, no doubt, the prospect of selling more Veloce boxes to customers Mentor already has.

Traditional in-circuit emulation (ICE) was confined to the lab. Various peripherals would be hard-wired to the box. Shifting (or time-sharing) across multiple projects was difficult locally and extremely hard where design teams were split across multiple sites. And the market was historically very hardware-led; software teams would find emulator time was jealously guarded.

Within EVP, Mentor’s VirtualLab peripherals can now instead sit as a Linux-blade in a data center alongside an emulator linked into a company’s network, all accessible as appropriate through one central corporate connection. That much clutter has gone.

As a result, albeit depending on capacity, numerous designs can use a data center-based emulator simultaneously or according to, say, different global time zones. OS3 includes an Enterprise Server which manages that access.

Maximizing emulator use and access has also been factored into development of the new Codelink software debugger. As well as now being the same across different verification engines, this now also has a ‘replay’ function. Here, a software-led emulation can be run once and then dumped for external debug in Codelink as a trace file.

Here, the ‘traditional’ configuration would have involved a software debug expert sitting at the emulator connected over JTAG at 1MHz. Now the work can be done by about 10 simultaneous users offline in a 100MHz debug environment.

Road tested

The EVP environment has been developed in conjunction with a number of Tier One users, including STMicroelectronics. Mentor says productivity improvements in the range from 400X to 10,000X have been achieved.

The company also claims that the EVP’s integration of the Questa and Veloce environments offer a ‘fast path to >1,000X acceleration’. The integration of the two now means that porting is easier and there should be no loss of functionality.

The Veloce OS3 operating system is available for both current and some earlier generations of the emulator. Existing customers do not necessarily need to buy a new box to already start taking advantage of the new features.

General availability is June 2014, so expect the EVP to be one of Mentor’s flagships at this year’s Design Automation Conference.