Real Intent’s Ascent XV at the ‘fuzzy’ boundary between design and verificiation

Real Intent has unveiled a number of major performance enhancements to its Ascent XV (X-Verification System) tool. Taken together they once more raise the question: where does design now end and verification start?

The five headline claims for the updated suite – available for download now – are as follows:

- A 10X faster runtime in reset and retention-flop optimization to reach toward complete initialization with minimal hardware and routing requirements, resulting in area and power savings.

- Enhanced reporting of reset audit information and counts of X-sources for easier debug.

- Greater integration with the Synopsys Verdi3 debug environment with new highlighting of X-sources and X-propagation on design schematics.

- SystemVerilog 1800-2009 language support for even easier adoption into existing design flows.

- Support for machines running the operating system SUSE Linux Enterprise Server 11 and above.

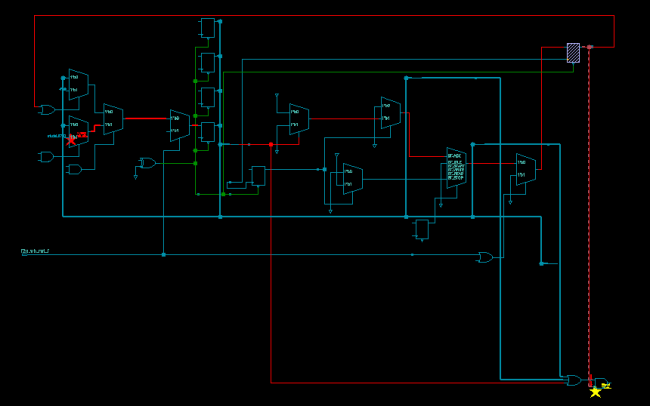

This screenshot shows an example of the Verdi integration. Verdi is showing a pruned schematic with annotations.

The red X on the far-left is the source of the ‘X’ being propagated. The Yellow X on the bottom right is an X-sensitive logic element that Ascent XV has identified as sensitive to the X-source.

Figure 1 Ascent XV debug in the Verdi3 environment (Source: Real Intent)

The important design challenges being targeted by Ascent XV are well recognized.

Striking the right balance between X-optimism and X-pessimism before entering any stage of simulation is fundamental to both design efficiency and sign-off.

Similarly, reset optimization is becoming a big challenge not just because of the increasing number of clock domains, but also the degree to which power management is making such schemes ever more complex. Resets, though, are costly bits of logic; you need to minimize them – so informed pre-simulation reviews and adjustments make a lot of sense.

The time lost if related bugs and other issues slip through – particularly if they enforce lengthy gate-level simulation – is one thing. They can lead to full respins. So you want to catch them early.

Lisa Piper, Real Intent’s Technical Marketing Manager, offers a further overview of the thinking behind and features in the new Ascent XV in this video. Lisa also recently looked at the importance of ‘smart reporting’ in a Tech Design Forum Expert Insight.

Ascent XV and merging roles

The upgraded Ascent XV highlights what is almost a philosophical shift, wider than one reflected just by Real Intent’s offerings. It is the convergence of various roles within the design flow. Just ahead of this launch, we spoke to Pranav Ashar, Real Intent’s CTO. We’ll be publishing more of that interview soon, but a couple of comments stood out in the light of today’s announcement.

“Simulation,” he said, “is a last resort. It largely comes about because of things that we do not understand.” So, as we do come to understand them, developing the heuristics and related algorithms to pull them out of the simulation stage, we can get greater efficiency. In Ashar’s words, “The theme in Ascent is all about preparing for simulation so that we make it meaningful.”

His second comment was this: “When you have a lot of complexity in a big system, you don’t want to do a lot of separate design and verification; you want to interweave it. It’s almost natural that the boundary is getting fuzzy.”

Not perhaps in itself an earth-shattering observation right now. We are all familiar with the consequences of increasing design complexity. But does it still prompt us to think less of ‘preparing’ for simulation and more about ‘pre-empting’ it?

Given that, in whose hands might a design manager place a tool like Ascent XV (or indeed Real Intent’s Meridian clock domain crossing tools), the design engineer or his counterpart in verification? The answer is probably both. That’s what the features in this new Ascent release suggest.

The verification engineer, the ‘traditional’ user, will be the one with the better understanding of X-related issues. But when it comes to resets, power management schemes and proliferating clocks, maybe the reports tools like Ascent XV produces are better reviewed by the designer.

Beyond that, an important objective for Ascent XV is measuring the various steps along the design flow, and the impact of that data on broader project management.

As noted, Pranav had a lot of interesting thoughts around this issue that we’ll be looking at as part of a new series on these elisions between traditional boundaries throughout the design flow, not just on the hardware side. Check back for more from him and other senior industry executives over the next few weeks.