December 1, 2008

The article describes how methodologies such as graph-based intelligent testbench automation will help engineers efficiently create verification scenarios and stimuli. This is a powerful way of enhancing advanced verification environments and reducing common verification headaches (e.g., reaching coverage goals). Such strategies can help to free up resources, in terms of time, people and hardware, so […]

December 1, 2008

This quarter’s issue leans slightly more toward coverage of incoming technologies than usual. Given the state of the economy around us, it can hardly hurt to look to a better future. At the same time, wise men in these new fields do seem quite keen on bringing us all down to earth. Consider: Professor Andre […]

Article | Tags:

November 1, 2008

This special edition of EDA Tech Forum Journal concentrates on PCB design. It’s an exciting area technologically right now, and we hope that the editorial content reflects that. One theme that kept emerging was that many of the contributors believe their discipline is at some sort of tipping point. And these changes don’t just come […]

Article | Tags:

November 1, 2008

Floorplanning informed by thermal analysis can significantly improve PCB layouts, writes Robin Bornoff The number of PCB design constraints seems ever increasing. The risk that a design will fail either functional performance or reliability goals grows for each generation. One increasingly popular trade-off addresses a balance between thermal compliance and signal integrity. Components with high […]

November 1, 2008

The PCB design team on Alcatel Shanghai Bell’s recently introduced A7510 Media Gateway product was given only seven weeks to complete its task against an original estimate of 13 weeks. The article describes how the team added new members and adopted a concurrent design strategy to not merely meet but beat the tightened deadline. Specific […]

November 1, 2008

New PCB tools have the intelligence to cut time and cost, explains Mark Forbes As far back as Marconi himself, RF design has been seen as having a touch of magic associated with it. Designs that looked just fine on paper would often require empirical tweaks to make them work properly. Until recently, even circuits […]

November 1, 2008

The contributor supplies high-end military communications systems to both the US and Canadian Navies and here describes the development of a new methodology and also a new backplane for a system that is now being retrofitted onto all ships in Canada’s fleet. The project represented a tipping point. In specific terms, the changes were undertaken […]

November 1, 2008

OSMOSIS is a super-fast optical switch developed through the Advanced Simulation and Computing program. The article describes the strategies adopted by the IBM team charged with designing the Central Scheduler board for the project. The design was of a far greater complexity than the team had previously encountered, and as a result, developed new pre-preparation […]

November 1, 2008

What impact do HDI via structures have on PCB design metrics? Andy Kowalewski describes a recent experiment. A PCB’s density has traditionally been seen as a function of the trace and space geometry and the number of signal layers. Emerging technologies such as microvias and buildup fabrication may force us to rethink this formula. In […]

November 1, 2008

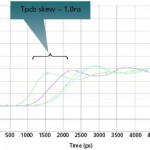

This paper builds on “Timing Numbers In ICX – What do we do with them?” [1]—a paper presented at the 2006 Mentor Graphics User2User conference (and now available for download at the journal’s Web site, www.edatechforum.com). The original paper focused on the need for timing analysis and the theory behind it; this paper takes a […]