Tessent Streaming Scan Network to shrink SoC test writing and runtimes

Mentor, a Siemens business, has unveiled an addition to its Tessent DFT family that aims to simplify set-up and cut test time by a factor of four.

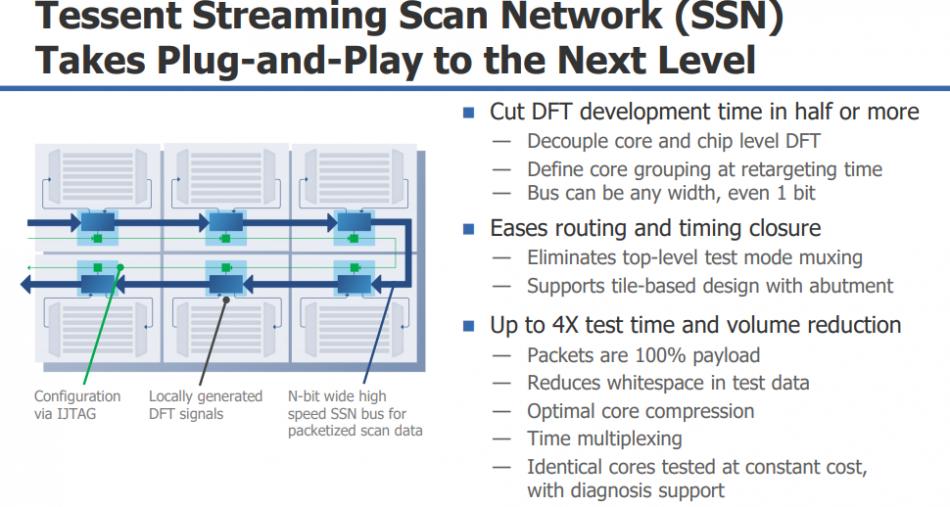

The new Tessent Streaming Scan Network uses a bus-based architecture for packetized scan test data distribution across any number of cores simultaneously. The technology inside the software allows for high-speed data distribution, manages imbalances between cores under test, and supports test across any number of identical cores with a constant cost.

Figure 1. Tessent Streaming Scan Network distributes packetized scan test data to multiple cores across a synchronous bus (Mentor)

There is a a plug-and-play interface in each core to simplify scan timing closure and the software has been optimized for abutted tiles.

In essence, Tessent Streaming Scan Network is designed to allow engineers to work with easier-to-assemble bottom-up flows while achieving the levels of analysis required for complex designs in markets such as AI.

At the heart of the software are host nodes in each design block that can be networked together. They distribute data between the network and the test structures, While the software automates the implementation, pattern generation, and failure reverse mapping process. Each block can be individually optimized based on this approach.

Overall, Mentor believes that its latest features not only have immediate value but are futureproofed against increasing design complexity.

“With the Tessent Streaming Scan Network, our customers can be ready for the designs of tomorrow, while slashing test implementation effort and simultaneously optimizing manufacturing test cost today,” said Brady Benware, vice president and general manager of Tessent Silicon Lifecycle Solutions.

The launch coincides with the opening of the 2020 International Test Conference as a virtual event. Engineers from Intel and Mentor will discuss the software’s use of SSN technology at a paper during ITC: “Streaming Scan Network (SSN): An Efficient Packetized Data Network for Testing of Complex SoCs.”

One conclusion from the paper reads: ““Intel evaluated SSN and compared it to STF as well as to conventional pin-muxed access. SSN was found to reduce the test data volume by 36% and 43%, respectively. It reduced test cycles by 16% and 43%, respectively. Steps in the design and retargeting flow were between 10x – 20x faster with SSN compared to STF”