Automating the pain out of clock domain crossing verification

Clock-domain crossing is the second most common source of respins. Avoiding the threat of issues arising due to metastability and X-propagation has required complex and time-consuming formal verification and simulation strategies. Many of these are manual when it comes to setup and/or debug, and the quality of the results shows room for improvement.

A new methodology addresses how some of that effort can be reduced with regard to protocols within the synchronizers necessarily placed in CDC paths on the ever-increasing number of designs that have multiple asynchronous clocks.

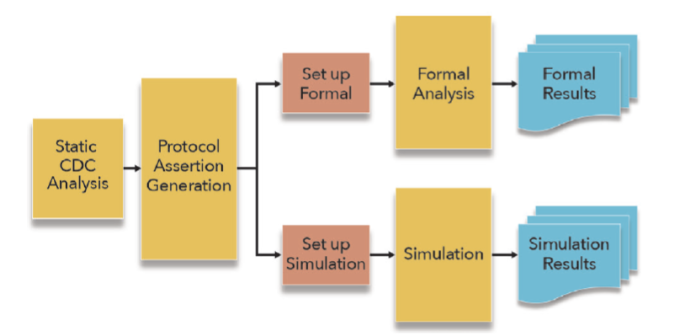

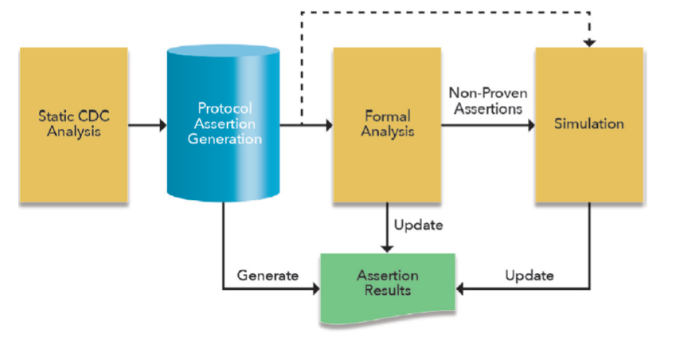

It proposes automating much of the effort and a comparison of the existing methodology and the one proposed is shown in Figures 1 and 2.

Developers Sukriti Bisht, Sulabh Kumar Khare, Ashish Hari, and Kurt Takara from Mentor, a Siemens business, propose “the automated propagation of setup from CDC to Formal and Simulation tools to help reduce the time and manual effort required in setting the design. This propagated setup includes design settings like clocks, resets, constants, port clock-domains, amongst others that are easily available at the CDC step. This automation ensures easy and correct propagation of setup without the hurdles of technical expertise required on the engineer’s part to set up each tool’s environments.”

They also discuss a strategy for harvesting better quality results from the process: “The protocol assertion generation step inserts hooks into Formal and Simulation to get insights into the status of each assertion. These insights help to correlate the Formal and Simulation results back to the associated CDC paths. This helps ensure that design and verification engineers can view the dynamic verification status of each CDC path.”

The proposed methodology was applied to a number of designs up to 30 million gates. For example, using the automated strategy cut setup time for CDC protocol verification using formal techniques from over five weeks to just one.

The methodology is described in full in Don’t Forget the Protocol! A CDC Protocol Methodology to Avoid Bugs in Silicon within DVCon proceedings.

Co-author Kurt Takara discusses an overarching CDC methodology for FPGA and SoC designs in a webinar that also refers to this research.