SAR-VCO combo tunes RF receiver power on 16nm

Researchers from the University of California at Berkeley and Intel teamed up to develop an energy-tuneable RF front-end on a digital finFET process with no need for analog process options.

Describing the work at the VLSI Circuits Symposium in Hawaii this week (19 June, 2018), UC Berkeley PhD student Amy Whitcombe said there were a couple of motivations for the work. One was to build a configurable receiver that would offer the potential for trading energy against performance. “The configurability provides potential for power savings of more than 2.5 times,” she said.

The other motivation was to take advantage of digital CMOS for scalability, allowing implementation on a standard 16nm finFET process.

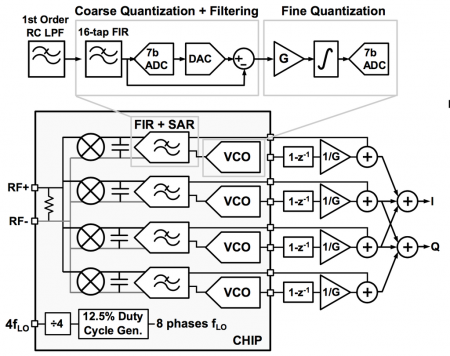

Image Architecture of the SAR+VCO RF front-end

“The idea of software-defined radio has been around for decades but it’s difficult to implement because you need a very high-performance ADC. If there is no mixer prior to the ADC, you need a very high ADC sampling rate,” Whitcombe noted. “A pipelined ADC achieves this but it burns power. Others use the delta-sigma topology. This achieves good linearity but it requires high-performance analog blocks.”

The UC Berkeley/Intel team’s answer was to combine four four-way interleaved successive-approximation (SAR) converters with a voltage-controlled oscillator (VCO) acting as a low-order sigma-delta converer.

The SAR and VCO do not have to be used together. If there are no significant blocking signals, the core can fall back to run with the VCO as the main converter, fed by a coarse SAR converter in each of the four subblocks that samples into a digitally tuneable capacitor. When the SAR is fully activated, a extra 128 capacitors in each sub-ADC are used but they only sample in one out of 16 cycles produced by a local oscillator. This has the effect of buildng a basic FIR filter and provides a way to set the frequency response of the converter.

On its own the VCO converter can run at a slightly lower voltage and offers a signal to noise and distortion ratio of 47dB. This improves to 60dB when the SAR stage is used.

“Noise is the main limitation of this work because we don’t have a dedicated LNA [low-noise amplifier],” Whitcombe said.