TSMC encapsulates CoWoS for supersized SiP

Foundry TSMC used encapsulation and process tuning to reduce the chance of warping with its second-generation chip-on-wafer-on-substrate (CoWoS) 3DIC packaging technology.

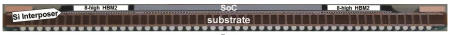

In a paper at the recent VLSI Technology Symposium in Kyoto, Japan, the company claimed it had pushed the area of the silicon substrate for the wafer-level system-in-package (SiP) to 1200mm2. To define the metal interconnect between then core SoC and as many as six memory stacks, the company used two passes on a lithographic stepper with stitching used to continue the interconnects across the reticle boundary. The lines themselves were 0.4um wide on a 0.4um pitch. Electrical analysis by the company indicated the stitched lines did not suffer from increased resistance.

Although the SiP coupled eight-layer HBM2 memory stacks with a single-layer SoC, TSMC matched the die thickness in the final package to ensure the backsides of all of them would have a good interface to heatsinks, to support use in high-performance computing systems. According to the company, a CoWoS-2 product with 16Gbyte deployed in HBM2 stacks reached a total memory bandwidth of 720Gbyte/s.

Image Optical cross-section of one of the CoWoS2 test vehicles

TSMC performed simulations of mechanical stress with and without encapsulation. The engineering team found encapsulation distributed stress more evenly. This is particularly important for multidie stacks because the overall stress increases with thickness.

TSMC’s engineers said the team performed a number of JEDEC qualification tests for reliability. The test vehicle formally passed qualification items that included moisture sensitive level 3 (MSL3), high temperature storage (HTS), temperature cycling classification B (TCB), and unbiased highly accelerated stress testing (u-HAST).