Master the verification challenge of PCIe-based NVMe storage

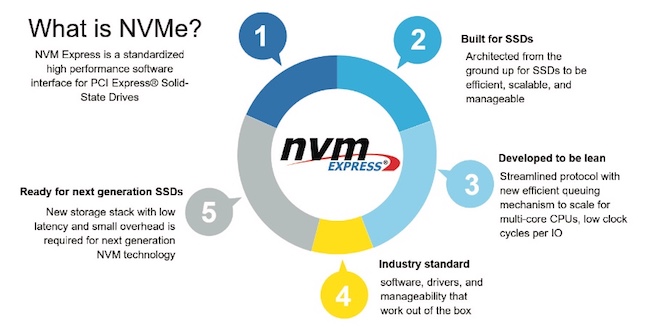

The NVM Express (NVMe) standard is stimulating a new wave of more powerful mass storage devices. But for all its strengths, it also sets new challenges for verification

An increasing number of analysts expects PCI Express (PCIe)-based NVMe to become the leading interface standard for storage. It offers high performance at low latency. The technology has specifically been developed to chart a scalable path from hard-disk drives toward the ubiquitous use of more efficient solid-state drives.

For example, NVMe demonstrations have already reached 1M IOPs; Serial ATA topped out at 200,000. Much higher bandwidths are also available.

NVMe also has a great many advantages in terms of both efficiency and performance. Only one MIMO register write is needed in the command submission path. There is support for multiple namespaces. The command set has been made more streamlined.

Meanwhile, and particularly important, the specification has been developed by and is supported through an open industry consortium.

Sounds great. But, as a new Mentor technical paper notes, “Considering the many complex features supported by the NVMe specification, it is no surprise that the verification effort is enormous.”

Author Saurabh Sharma, a member of the consulting staff at Mentor, A Siemens Business, describes how to relieve this burden in ‘Five common pitfalls to avoid while verifying PCIe-based NVMe controllers’.

Your checklist for NVMe verification

The five overarching problems he identifies are.

- Not testing register properties;

- Failing to explore queue-related non-trivial scenarios;

- Not focusing on controllers attached to PCIe virtual functions;

- Overlooking interrupt and its mask handling complexity; and

- Misunderstanding metadata concepts.

The fine grain analysis that needs to accompany each of these issues is set out fully in Sharma’s article. Particular reference is made to the use of verification IP (here specifically from Mentor’s Questa VIP sequence library) to help complete the complex work more efficiently.

Sharma’s goal is straightforward. “Verification engineers must be aware of the common pitfalls experienced while verifying PCIe-based NVMe controllers,” he writes.

“By knowing the areas where the probability of these occurring is highest, engineers can create a verification plan checklist to avoid them with confidence.”