Toward easier, faster test pattern simulation

A big problem with validating test patterns is that traditional strategies can take a long time to run. They can either clog up the design flow or – because of their raw size – get cut back so that the actual test process may not be as comprehensive as it should be. The one thing we all do know is that test pattern simulation is essential.

Mentor Graphics introduced a DFT App for its market-leading Veloce emulator in February (alongside a series of other enhancements we covered at the time). Simplifying and speeding the validation task is the App’s primary reason to be.

The company has now followed up that specific launch by publishing a technical primer on ‘Accelerating Design-For-Test Pattern Simulation’.

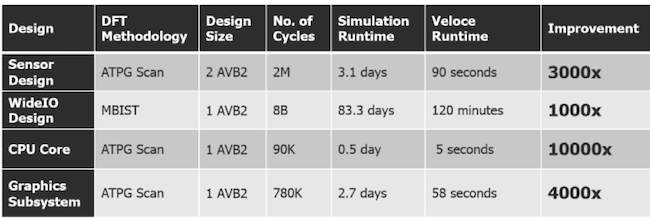

One of the key metrics in the paper looks at Veloce’s performance running test pattern simulations compared to simple software simulation. Mentor is claiming results like those in Figure 1 for a range of possible designs.

As with other EDA Apps, the ideas behind the Veloce family are straightforward: Offer various useful tasks that engineers buy into as they need, then make each of those tasks easy to accomplish.

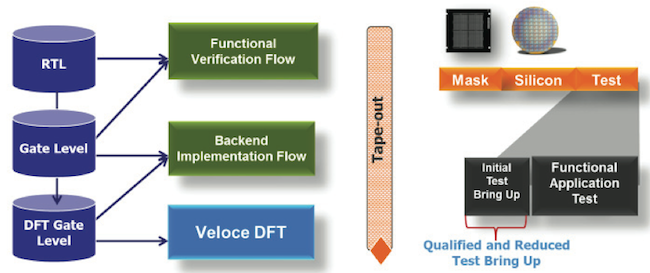

The Mentor paper describes how a DFT simulation flow based on using emulation hardware acceleration can instill greater confidence in test patterns before first silicon arrives. You can see an overview of the basic process in Figure 2.

The paper also describes the pattern compilation and runtime flows in more detail.

Alongside DFT, the other recently launched Veloce Apps for the Mentor emulation family cover in-circuit emulation (Deterministic ICE) and bringing greater efficiency to the bridge between the workstation and the emulator (FastPath).

The abstract for the paper reads: “The Veloce DFT App presents a true ‘left shift’ improvement for a traditional chip design schedule that requires comprehensive gate-level simulations to develop ATPG, BIST, or functional patterns. It enables running complete patterns for DFT verification in a reasonable time to shorten the pattern development cycle.

“As part of the Veloce ecosystem, it brings along a host of other powerful apps and features in the context of DFT infrastructure validation. The high performance of emulation adds more “simulation cycles,” pulling the DFT schedule to within the time the project management has allocated. This means quicker time-to-market and increased yield, which means higher profits.”