On-chip interconnect startup uses network theory to sidestep deadlocks

A startup aims to cut SoC integration time using theories developed for much larger computer networks. NetSpeed Systems has developed in addition to a network-on-chip (NoC) architecture a set of tools designed to synthesise the best type of network for a given SoC, one that would be free of deadlocks and balance power with performance.

Sundari Mitra, CEO of NetSpeed said the company is working on the basis that NoC implementation needs more than interconnect IP and interfaces. “What generated the idea is that guys were calling them NoC solutions but I didn’t see any of their work involving the theories developed by the networking industry. I said, ‘hey, the networking industry has already solved many of these problems already’. They found they were getting too much congestion from crossbars. So they came up with traffic management as an alternative. I thought, can’t that be adapted to the SoC environment?”

Similarly, computer network theories developed 20 years ago and dating back to work in the 1980s by computer scientists such as Professor Bill Dally of Stanford University dealt with issues such as deadlock in larger networks. This led to the development of efficient networks based on wormhole routing that employed routing-based mechanisms for avoiding deadlocks.

NoC generator

Like these systems, the Orion NoC architecture developed by NetSpeed that was unveiled at the Hot Chips conference in 2013 and the Gemini cache-coherent NoC include design to provide the combination of wormhole routing and graph-based routing analysis to create a deadlock-free interconnect.

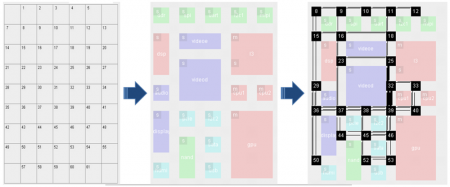

Image For early analysis, a floorplan can be assembled on a 2D grid to generate a candidate NoC

“A next-generation IC is really a sea of IPs. It marks a progression in the complexity of the SoC and a shift in what is required in the SoC. A lot of the system analysis methodologies that are required to globally optimize the SoC implementation are missing,” said Mitra. “It needs to be very flexible and configurable IP. That will give the power of differentiation. This is a true on-chip network that follows the principles built up over the past 20 years,” said Mitra.

“NetSpeed has created an SoC-level synthesis platform. We take in power and performance and area metrics. It points to a library of IP blocks. It creates a massive dependency graph which it then solves to come up with a definition of the on-chip interconnect. We model the SoC graph using mathematical equations.

“Competitors give you a NoC. But we are responsible for figuring out the algorithms the network will use, the number of channels and do that automatically.”

The tools take in system descriptions that then evaluate the types of cache coherency pieces of the NoC need to support. For example, if the traffic between cores is not a bottleneck, users can decide to make the implementation back off from a full MOESI protocol – which is good for reducing intercache traffic – to a simpler three- or four-state protocol.

IP compatibility

To provide compatibility with AXI3 and AXI4 interfaces, Mitra said: “We provide a shim layer and perform the protocol conversion at packet level. We support ARM-based protocols and other proprietary implementations.

Anush Mohandass, vice president of business development at NetSpeed, said: “At the beginning we expect the designer to give some workload models, providing attributes such as average and peak bandwidths for different transactions. As and when they get more understanding and get the different traffic traces from simulation, they can provide more constraints.”

Users can provide source floorplans for the tool to use, or it can use information from traffic and constraints to provide a floorplan for IC implementation tools based on techniques such as simulated annealing – similar to the placement algorithms used for more mature IC processes.

“We can provide a logically optimized floorplan but that’s not necessarily the right answer because the team may have ideas about the placement of I/Os.” Although it is not yet supported, “going forward we can provide layout information in the form of DEF files”, said Mitra.

Today, the output provides RTL and constraints for synthesis, excluding those that are needed for mapping to a specific process technology.

Although it contains a strong tools element NetSpeed has chosen an IP-based business model, Mitra said. “The configuration platform is given to customers. When the configuration is generated, that’s when they pay. It’s very similar to the model used by Denali or Tensilica, with a licence fee and a royalty element.

“There are actual customers using our IP,” said Mitra, pointing to some sizeable but as yet unnamed users in networking and mobile systems.

As well as Arteris and Sonics, NetSpeed is among the NoC specialists exhibiting at DAC 2014.