Cadence building photonics environment around Virtuoso

Cadence Design Systems is gearing up for a flow that the company believes will make it possible to bring greater predictability to photonics design.

Cadence distinguished engineer Gilles Lamant, who has been building the photonics flow with third-party suppliers Lumerical and Phoenix Software, says the aim is to build an environment that can cope with any sort of photonic design. But the company sees demand for photonics picking up in various sectors largely because of concerns over the speed and energy consumption of copper interconnect.

“We are starting to see data centers as a driver,” Lamant said, with photonic interconnect starting to move inside the servers themselves for processor-to-processor communication through photonic interposers. “The one thing they can’t work around is that there is a limited bandwidth on copper. It will be very hard to beat the bandwidth of fibre.

“Also, automotive and aerospace are driving RF over fibre,” Lamant added, pointing to the need to save weight and with it fuel consumption by replacing bulky copper wiring harnesses with fiber communications. Lidar arrays for advanced driver assistance system (ADAS) designs provides another potential growth market as teams try to reduce the size of the equipment down to the scale now enjoyed by 70GHz-plus radar. “There is a sense that the market is ready.

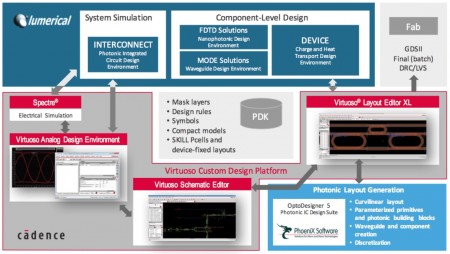

Image Cadence's proposed photonics design environment

“From a tool perspective we are trying to look at the complete photonics market. We are not building tools that are specialised in one technology, so it’s aimed at just silicon or indium phosphide, or trying to limit the domain or applicability of the solution,” Lamant said.

The push for a photonic design environment has come from larger customers, Lamant explained: “They need to have a way to design photonics so that it’s not separate from electronics, using techniques like top-down design that are used in mainstream electronics. That approach today is foreign to photonics designers. They tend to have an ad hoc methodology.

“The big companies come to us and say it’s not predictable: they can’t put a schedule on it. They said: ‘Make it look more like a normal [electronics] design flow’. The idea is to have concept from electronics design flow. But bring in the specificities of the photonics world,” he explains.

Autumn launch

With the aim of getting the first copies into the hands of designers at customers in October, Cadence has worked with specialists Lumerical and Phoenix to build a flow around Cadence’s own Virtuoso schematics and layout and Spectre simulation tools. Lamant said one of the aims is to provide photonics teams with the ability to build much of the design using schematic capture early on, moving onto to layout later, in contrast to today’s prototyping-heavy projects.

“Lumerical released the first cosimulation solution this May. In this case, Spectre manages the time steps but the photonics simulator is built into the environment. The Lumerical simulator synchronises with the time steps [generated by Spectre],” Lamant explained.

“One of the reasons why people wanted simulation feedback loops is for controlling for temperature changes. When you have an optical-only simulation or have sequential simulation, you can’t get those feedback loops done easily. The feedback loop with Lumerical was a milestone in our collaboration.”

The Phoenix OptoDesigner 5 suite provides layout generation with support for curved objects and waveguide creation. “When you are right the waveguides need to back-annotate the S parameters [for electrical simulation],” Lamant said. “Once we have the basic plumbing there are many things we can work on to make sure that the design when it goes to the fab is validated in the same way as it has been for electronics for many years.”

Lamont said the process should not be compute intensive, although issues such as variability will increase the need for Monte Carlo simulation. The main compute bottleneck is 3D extraction when the photonic component models are created. “But out of the you get a compact model that should not be very time-consuming,” he noted.