Creating the right simulation build flow

Which simulation build flow will be best for your next SoC project? A new technical article describes the options, the projects that best suit each one, and how you can put your preferred choice into action using the Questa simulator.

Broadly speaking, design managers face these incremental options:

Lump Sum Build: Perhaps best used these days at the small-to-medium sub-system level.

Partitioned Compile: A better option where IP integration and testbench layering are necessary and well suited to larger sub-systems.

Parallel Compile: Exploiting the use of more cores in parallel for simulation to raise run performance.

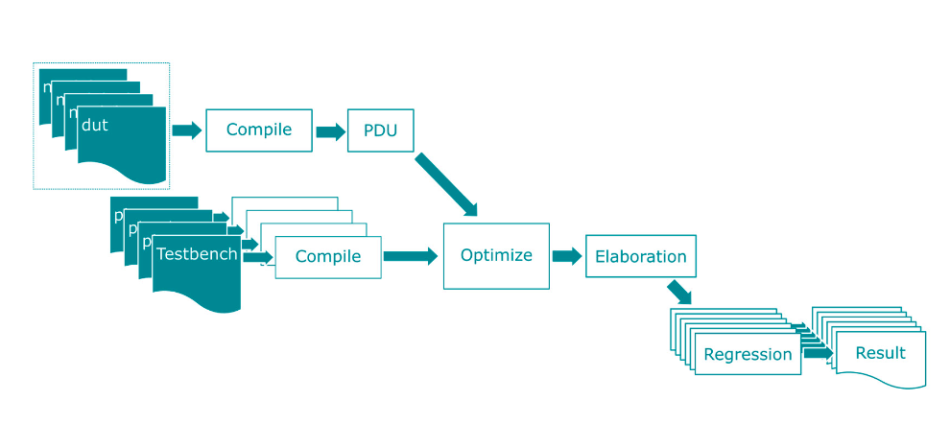

Pre-optimized Design Units: These compile large design hierarchies into single units that are optimized independently and then plugged into the full design run.

Elaboration Flow: A Questa feature designed to prevent re-elaboration across multiple runs that is particularly valuable for regressions.

Figure 1. A full Elaboration Flow combining all the options for simulation (Siemens EDA – click to enlarge)

Author Neil Johnson, of Siemens Digital Industries Software, describes how these options can be assembled using ‘qrun’, a recently added command-line front end for Questa that upgrades and streamlines the previous and long-established three-step build/stimulate flow (‘vlog’, ‘vopt’ and ‘vsim’) in the software.

To familiarize both new and existing users with the ‘qrun’ option, Johnson sets out typical code fragments for each of the build flow options.

“Whether you’re verifying a small sub-system as a one- person team or an entire SoC with a much larger team, the combination of compiled library partitioning, PDUs, parallelism and elaboration flow are the tools you need for an optimal build flow and reduced build times,” Johnson says.

Expediting Simulation Turnaround Time with Incremental Build Flows is available for download here.