Use-cases drive high-level verification tool

Cadence Design Systems has released a tool intended to automate the creation of scenario-driven tests to better exercise complex intellectual property (IP) and system-on-chip (SoC) designs.

Frank Schirrmeister, senior director at Cadence, said: “We are adding to the traditional bottom-up view of verifying IP: adding scenario- and software-driven verification, a top-down view.”

The Perspec System Verifier employs use-case descriptions built using the Unified Modeling Language (UML) to generate tests of different user-level scenarios, such as watching a video while it is being uploaded to storage in the cloud, from the C functions that can used to implement the service. A constraint solver builds tests that include the random generation of attributes to provide a harness similar to that used in constrained-random simulation in common use at the hardware level.

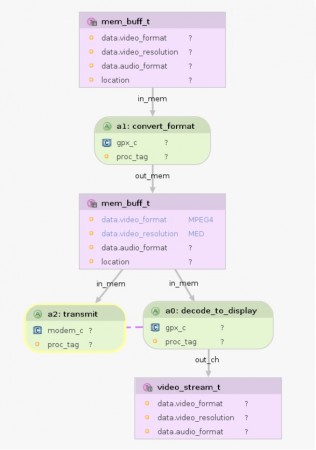

Image A video streaming and transmission use-case in Perspec

For example, from the video use case, the solver may randomise the key attributes of a video buffer, select a video format and randomize aspects of the video stream. The software takes the C functions identified in the use-case to provide test software that will act as stimuli for simulation or emulation. The tool also creates and prunes coverage models for reachable scenarios.

“Today’s verification teams face a challenge in that the bottom-up approach to IP verification does not extend to the SoC level, and they are looking for an opportunity to move to top-down scenario-based verification in order to extend traditional approaches like UVM and achieve better coverage,” said Charlie Huang, executive vice president of worldwide field operations and the system and verification group at Cadence. “With its SoC-level constraint-solving technology, Perspec System Verifier is enabling our customers to create tests previously not feasible.”