Synopsys combines cell-aware, slack-based test to find transient defects, adds eFlash support

Synopsys has updated its TetraMAX ATPG tool to do a better job of finding transient defects that would otherwise go undetected in IC manufacturing processes.

The company says that at advanced nodes, such as finFET processes, manufacturing issues such as shorts between metal lines, open vias, open fins, and lithography violations are becoming more prevalent.

At the same time, applications such as medical and automotive electronics are demanding greater levels of reliability, leading to demands for more effective testing of designs built on established process nodes.

According to data from STMicroelectronics and Synopsys’ regular customer survey, more than half of the defects that cause such transient faults are not found with traditional at-speed tests. Many of the defects are ‘hidden’ within library cells, where traditional ATPG approaches may leave the defects unstimulated and therefore unobservable.

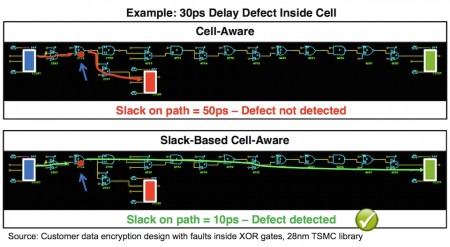

Even if these defects can be properly stimulated, they only cause very short signal delays, whose effect can be absorbed by the slack available on short signal paths to the nearest register. The result is that the defect can go undetected, but still cause a problem when it delays a signal on a longer path with less slack.

According to Robert Ruiz, senior product marketing manager at Synopsys, the way to find such defects is to combine two techniques: cell-aware and slack-based testing.

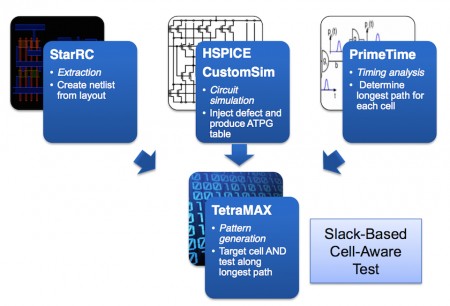

Figure 1 A combination of extraction, simulation and timing analysis enables TetraMAX to target cells and test along the longest paths (Source: Synopsys)

Cell-aware testing uses Synopsys extractors and circuit simulators to model the behaviour of defective cells, so that the TetraMAX ATPG tools can then generate patterns that will stimulate such cells to reveal any similar defects. This means that the tool can do a better job of finding defects within cells.

The second step is to use data from Synopsys’ PrimeTime static timing signoff solution to find which paths downstream of a potentially faulty cell have the least slack and therefore are most sensitive to even short delays.

Figure 2 Transient faults can be masked by paths with lots of slack. Checking the impact of a transient on a path with less slack can may be more effective (Source: Synopsys)

By being able to stimulate in-cell faults more effectively, and checking the impact of their faults on the most sensitive paths, coverage of these transient faults can be improved.

In one set of customer data presented at the Synopsys test SIG at ITC this week, a slack-based test strategy achieved 16.4% coverage of defects within a cell, while a slack-based cell-aware approach achieved 67.4% coverage. Interestingly, the number of patterns necessary to achieve this fell from 6119 with the first approach to 121 with the second.

Embedded flash test

Synopsys has also added capabilities for specifying self-testing embedded Flash arrays to its DesignWare STAR Memory System. The first vendor to support the capability is UMC with its 55nm CMOS process. Other processes from other vendors should follow.

The DesignWare STAR Memory System for Embedded Flash is an automated pre- and post-silicon memory test, diagnostic and repair solution that uses test algorithms optimised for embedded flash memories.

It enables designers to create areas of embedded Flash on their SoCs that can test themselves for the kind of failures particularly associated with embedded flash memories. Synopsys claims this can cut test costs by “20 per cent, at a conservative estimate” compared to the cost of using dedicated external testers, according to Savita Banerjee, senior product marketing manager, embedded test and repair at Synopsys.

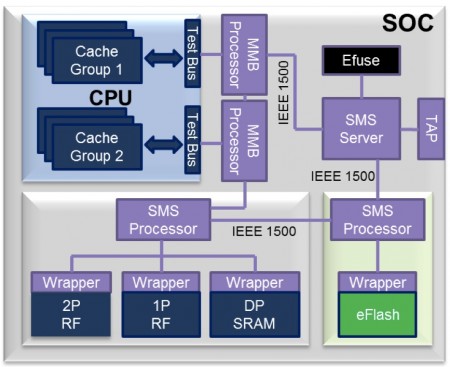

The STAR Memory System enables hierarchical generation and verification of the test and repair IP to be inserted into the SoC while maintaining the original design hierarchy. This approach enables existing design constraints and configuration files to be reused, saving development time. The post-silicon Yield Accelerator and Silicon Browser features can cut the time required for silicon bring-up and defect analysis for yield optimization.

Figure 3 How the eFlash test blocks can be integrated into a wider SoC memory test architecture (Source: Synopsys)

The system can also support remote diagnostics, so users can identify memory issues even when the memory is embedded in an SoC in a device that has already shipped to an end customer. Synopsys sees this as a useful facility for Internet of Things (IoT) application such as wearables and smart appliances, and in automotive safety systems.

“SoC designers for IoT and automotive devices must implement cost-effective features that enable efficient test and diagnostics for the full life cycle of their products,” said John Koeter, vice president of marketing for IP and prototyping at Synopsys.

The DesignWare STAR Memory System for Embedded Flash is available now for UMC’s 55nm process

Further information

More on the update to TetraMAX here.

More on the Synopsys synthesis-based test solution.

The eFlash press release is here.