SoC design gets hierarchical test strategy, improved compression; system design gains end-to-end IJTAG integration strategy

How do you manage the increasing test burden that comes with growing design complexity? Synopsys is launching a pair of tools this morning, to coincide with this week’s International Test Conference in Anaheim, which address just this issue.

The STAR Hierarchical System is an automated way to add hierarchical test structures to an SoC design. It provides the infrastructure to connect all the design-for-test (DFT) features of an SoC together in a coherent way, and then to coordinate how they test the chip. The tool is particularly focused on SoC designs that include IP blocks – Synopsys claims IP use is growing more than 50% per process node – but has facilities to manage other tasks such as trimming AMS circuits for yield. It integrates with other Synopsys tools, for example for testing memory or interface blocks.

The tool is based on stardards including the IEEE 1500 standard for embedded core test; the venerable IEEE 1149.1 test access and boundary scan architecture; and P1687, which allows for system-level access and control of on-chip test facilities. In this way Synopsys plans to leverage the test facilities already available in some IP blocks, and to provide a consistent way of encapsulating, addressing and controlling blocks that don’t have such standardised test facilities.

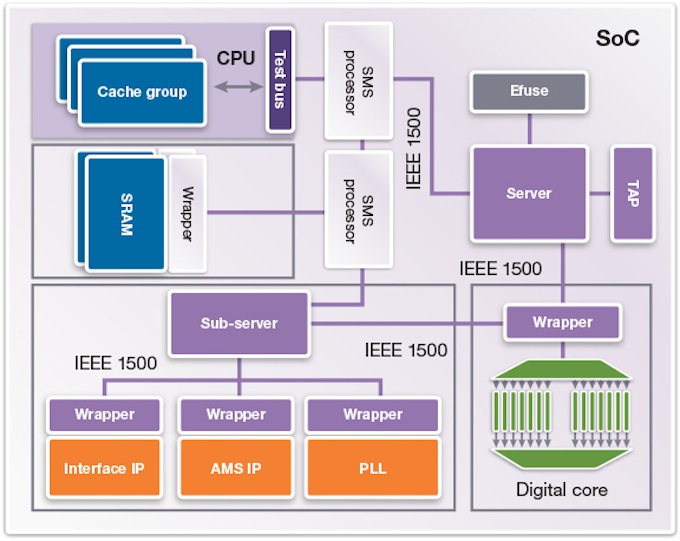

Figure 1 The tool includes test servers, a bus structure, interfaces, and wrappers (Source: Synopsys)

As the diagram shows, the tool will automatically create an IEEE1500-compliant test bus that accesses any blocks with the relevant interface directly. Blocks without a 1500 interface can be wrapped by the tool. An on-chip test server then coordinates how blocks are tested, for example to ensure that the overall chip power budget is not exceeded during test, or to enable certain blocks to be tested simultaneously yet independently. The tool can also instantiate sub-servers at a given level of the design’s hierarchy, so that all the blocks at that level can be tested and passed under a sub-server’s control, reducing the number of signals that need to be routed to, and controlled by, the top-level server.

Sandeep Kaushik, senior product marketing manager for embedded test and repair at Synopsys, said: “The STAR Hierarchical System is trying to solve that problem which customers can’t solve with ad hoc systems based on direct I/O, which would have a high impact on place and route.”

The hierarchical approach also means that any test patterns already developed at the IP and logic-block level can be reused within the SoC context, by passing them down through the test hierarchy and using the test server to isolate them as appropriate. This saves design teams the effort (and potential for unforced errors) of developing new test patterns to test each block from the SoC level.

Although this hierarchical approach should reduce the overall test signal traffic on a large SoC by localising some of the testing within blocks that have built-in self test facilities, or at a particular level of hierarchy, the pressure on test access ports is still rising. This is because of increasing design size, and the emergence of more subtle faults, such as finFET opens, which take more complex test patterns to isolate.

The second offering from Synopsys this week addresses this issue. DFTMAX Ultra is a new compression technology that the company says can increase test compression up to threefold.

According to Robert Ruiz, senior product marketing manager for test automation at Synopsys, one of the ways in which the compression has been improved is through better handling of unknown states: “Xs and compression don’t mix well and DFT MAX Ultra handles them more intelligently.”

The logic which handles the algorithms on chip has been improved so it can handle decompression and compression at the same time, and has also been pipelined for greater speed.

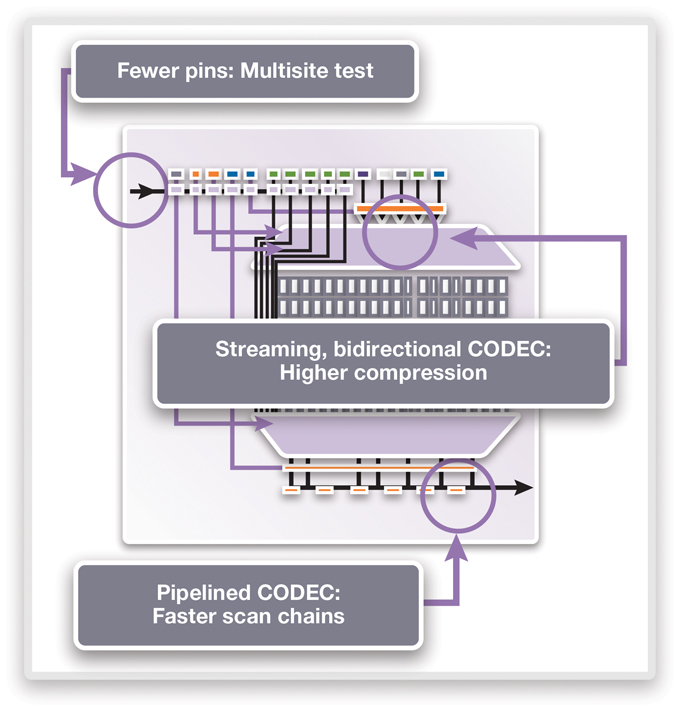

Figure 2 Pipelining the codec helps speed up scan chains and save access pins (Source: Synopsys)

According to Ruiz, most testers today can run at 100MHz and some can run at 200MHz. Synopsys customer research suggests that around half of the scan chains in use on current designs are only running at 50MHz, in part because of slow codecs.

Speeding up scan chains and improving test compression algorithms has a multiplicative effect on how quickly test patterns can be moved on and off chip. This helps counter the impact of the emergence of more complex faults, which can only be found using more complex test patterns. It can also be used as a way of reducing the number of test access pins a design uses: if you can double the bandwidth of a test port through pattern compression and faster decode logic, it gives you the option to halve the number of test port pins per chip.

Synopsys says that some designers are using this facility to reduce the number of test pins per chip, even down to just two (scan in and out), so that they can then test multiple devices at once on the tester.

Again, multiplying up the impact of increasing test compression through new algorithms, faster scan chains due to pipelined decode logic, and the opportunity this brings to test multiple devices at once, Synopsys claims that DFT MAX Ultra could cut test costs 20 to 30fold.

There are videos introducing the two products here.

*** Mentor Graphics is also taking advantage of ITC to announce full interoperability between its Tessent IJTAG chip-level IP integration product and ASSET InterTech’s ScanWorks platform for embedded instruments, which includes chip, circuit board and system-level IJTAG tools.

The combination of tools should enable designers to bring the operational and diagnostic features of any chip-level IP that includes P1867 facilities up to the board level for debug, validation and test.

Interoperability between the two tools is enabled by the IEEE P1687 standard’s Instrument Connection Language (ICL) and Procedural Description Language (PDL).

Kent Zetterberg, ASSET’s IJTAG product manager, said in a statement: “We’re working with Mentor to provide a seamless flow based on IJTAG from the IC design environment to the SoC and PCB debug, validation and test phase.”

The Tessent IJTAG tool reads ICL and PDL code delivered with third-party IP blocks and verifies that it complies with IEEE P1687. It then generates a logic network and associated ICL to integrate all the IP blocks in a design, and processes the PDL for each IP to create composite chip-level PDL. The ScanWorks product then reads chip-level ICL and PDL for use in chip debug and also retargets the PDL to a board or system-level interface.

Stephen Pateras, product marketing director at Mentor Graphics, added: “At ITC, Mentor and ASSET will demonstrate a design flow with full PDL/ICL interoperability to be delivered later in the year, synchronized with ratification of the IEEE P1687 IJTAG standard.”

Further information

More details about STAR Hierarchical System from Synopsys here.

More details about DFT MAX Ultra from Synopsys here.

More details on Mentor Graphics’ Tessent IJTAG tools here.

More on ScanWorks’ offerings here.

Sign up for more

If this was useful to you, why not make sure you’re getting our regular digests of Tech Design Forum’s technical content? Register and receive our newsletter free.