Tile-based integration of analog functions enables power controller family

Integration doesn’t have to be done at the nanometre scale to be interesting.

Power management IC company Active-Semi has just launched a range of ‘power application controllers’ using a tile-based integration strategy. The idea is to bring together the right set of digital microcontroller, analog and high-voltage functions to produce chips targeted at the needs of the (very large) motor control, LED lighting, power supplies, automotive electronics and renewable energy markets.

According to Alex XuCheng Wang, executive vice president at Active-Semi, the basic approach is to build a multichip module so that the digital, analog and high- voltage sections can be segregated onto different bits of silicon. The functionality of the analog die is predefined using a library of functions expressed on regular-shaped tiles so that they can be brought together in different combinations quickly.

“If customers want one more H bridge we can quickly add that because the gate driver is one more tile,” said Wang. “The analog die already has multiple tiles so we just have to make it a bit bigger.”

Another enabler of the approach is a patented bus linking the analog and digital parts of the system, and a separate bus within the analog block that connects all the tiles “so we can just unplug an analog front-end tile and add another tile alongside it.”

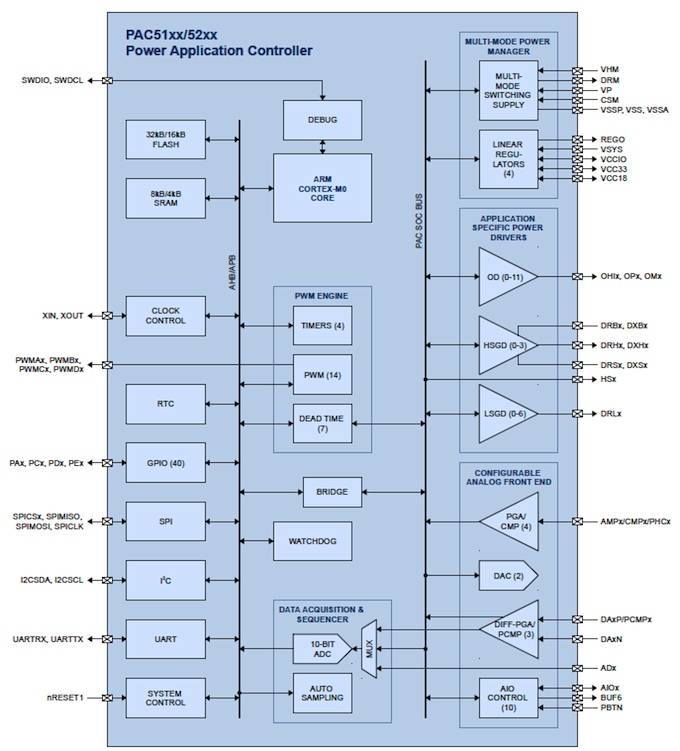

Here’s a look at the architecture diagram – note that the way that the functions are segregated in the diagram probably doesn’t reflect how they are split across the silicon die:

Figure 1The Active-Semi power controllers use a tile-based design approach to enable fast adaptation (Source: Active-Semi)

Of course, you’d have to be bringing huge volumes to Active-Semi to get them to produce a custom part for you. A canned quote from the press release suggests that that’s exactly what LG Elcctronics has done.

“We are very glad to see the level of integration in the PAC platform with the features highly optimized for power control and conversion product designs,” said KH Lee, manager and chief engineer, Energy Components for Home Appliance, at LG Electronics. “PAC is a very unique system chip platform that allows us to implement various high energy efficiency products with reduced time to market.”

For the standard products market, the tile-based analog design approach is really meant to enable the company quickly to develop the right set of analog functions for a vertical market.

The digital part of the device sports a 50MHz Cortex-M0 processor, with the usual array of attendant functions such as GPIO, UARTs and watchdog timers. The analog part of the chip can have up to 10 analog front-end I/O pins, and a variety of differential programmable gain amplifiers, single-ended programmable gain amplifiers, comparators and DACs. The power driver section includes low-side and high-side gate drivers, operating at up to 600V AC, plus a variety of open-drain drivers, configurable delays and fast fault protection.

Ten standard part numbers have already been defined with various combinations of these functions, the part numbers go up in decades, suggesting that there could be variants of each if there’s a sufficiently large market

Larry Blackledge, CEO of Active Semi, reckons that the tiled approach to the design could halve development times for new variants as well as reducing development costs by as much as 60%. As is always the case with these sorts of semi-custom offerings, it will be interesting to see whether the functional mix in the standard products will hit the right market sweet spots, and conversely, whether the cost and time involved in producing custom variants is low enough to make them of practical interest to real customers.

Steve Ohr, analog and power semiconductors analysts at Gartner, drew a parallel with the old linear array business, in which pre-fabricated chips carrying analog circuitry such as amplifiers would be metallized to create the functionality you wanted. (There was even a brief flirtation with ‘analog FPGAs’.)

“The trouble with the linear array business is that you never use all the functions built into the pre-fabricated chip, and your device winds up with significant amounts of unused chip area, and that increases your costs. You wind up using the array for prototypes, but the actual production version may involve a set of carefully matched – and price-reduced – discrete components.”