NI aims to bring design and production closer with chip-test plan

National Instruments plans to build an ecosystem around semiconductor test that could fill the missing link between the design process and production. The company launched at its annual NI Week conference in Austin, Texas this week (6 August) the first of a range of chip-test platforms that have been trialled by customers such as IDT as part of their own plans to reduce test cost.

The Semiconductor Test System (STS) is based on PXI-compatible hardware, which the company has sold for more than a decade as a platform for custom test equipment, and the LabView software.

Chris White, product development manager of semiconductor test at NI, said in a keynote session at the conference: “We are sitting on a massive collection of IP that is ideal for high-volume production test. But the number-one request we get is to make our capabilities easier to use. So we tied a bow around our capabilities and introduced our new Semiconductor Test System.”

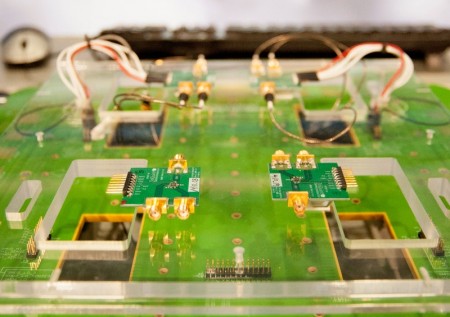

Image Chipmakers have used STS to enable multisite testing for higher throughput

Luke Schreier, senior manager of automated test marketing at NI, told Tech Design Forum the systems have defined fixtures and APIs to allow third parties as well as customers to provide specialized probe heads and test programs. “We have taken out the ambiguity so they can design for it,” he said.

White said a motivation for the STS is test time and cost: “The cost of manufacture has been declining but the cost of test has remained stubbornly flat.”

Rebeca Jimenez, vice president of worldwide test at IDT, said: “Our main challenge is reducing the cost of test and increasing test utilization.”

FPGAs on the PXI hardware are intended to run test programs to provide quicker mixed-signal tests. “Production guys say every millisecond counts. So instead of going to the processor to make decisions, we put the control in the FPGA,” said Schreier.

As well as test time, NI believes its approach will also reduce the time and cost of writing the test programs themselves by reusing IP developed during chip development. “The equipment you need to design for an RF system is going to look a lot like something you need to production test it,” Schreier claimed.

Earlier test development

Glen Peer, IDT test director, said: “We want to bridge the gap between product engineering and production test, and are using LabView for that. The challenge for us is keeping up with the designers. Our guys design so many parts and they are getting more and more complex very quickly.”

The problem up to now has been translating the development test routines into production-ready programs that generally use different hardware and software, said Schreier. “In the past, you had to buy something optimised for the bench or for the production line but not both. We wanted something that’s instrument-grade and high performance enough to keep up with production. We feel that this is ready to step up and help solve that problem.”

Nisha Ganwani, senior marketing manager of RF test at NI, said: “It will be less expensive to use the same instrument for your design process as for test because it will be easier to correlate with production.”

Peer said using LabView, IDT’s test operation for frequency-control products – the division that trialled the STS – is building up a library of test IP. “We have those libraries and we are moving development earlier in the process and into product engineering.”

Throughput improvements

The rigs developed by IDT on the STS are designed to test multiple parts at the same time. The current system – of which three are now in use in production – takes four parts at a time. Because the tests do not quite take the same amount of time, Peer said the throughput gain is not quite fourfold over a single-site tester but it is providing significant cuts in test cost.

Schreier said the long-term aim is to also help with post-silicon debug. Alignment of development and production test based on common PXI hardware has been used at Triquint to cut bring-up time from a couple of weeks to 24 hours, he said. “If you have an ATE platform that gives you different data to the bench-top instruments, it is going to take time to correlate the results. It’s a lot more efficient to use the same equipment.”