Synopsys claims latest Design Compiler shrinks existing netlist area, leakage up to 10%

Synopsys says it has adjusted the optimisation algorithms used in the 2013.12 release of Design Compiler Graphical, its flagship synthesis product, to achieve layouts with up to 10% less area and up to 10% less leakage than those synthesized with previous versions.

The company says the optimisations can be applied to existing gate-level netlists, as well as designs being synthesized from RTL for the first time.

“Customers can bring in an existing netlist, take it through our area optimisation step alone and seen an advantage,” said Gal Hasson, senior director for product marketing, RTL synthesis and test. “You just get a nice area and leakage improvement for free,” although starting afresh from the RTL may bring greater improvements.

Synopsys says the new optimisations are monotonic, that is area and leakage may improve without other factors, such as timing, being affected.

Hasson said that most of the improvements come from better logic optimizations, including mappings that are more targeted towards reducing area. These include breaking up large logical blocks in the netlist into combinations of smaller blocks which give the placer more room for manouevre. Hasson gave the example of test compression strategies, which use large multiplexers to connect the output of decompression logic to the rest of the circuit. Breaking the mux down into several smaller muxes eases placement and relieves the routing congestion that can happen when a large mux has to access many parts of a chip.

Other optimisations include greater sharing of logic among multiple operations, improving the handling of redundant logic, and working harder on managing congestion.

“You can synthesise certain RTL structures multiple ways and DC Graphical does it to reduce the amount of logic with a lot of internal interconnect,” said Hasson. “We made this part of the cost function of synthesis: meeting power, timing, area and having a netlist that is routable.”

Synthesis also handles multiple design corners and modes at once, to avoid designers ‘ping-ponging’ between a netlist that is optimized for one criterion at one design corner in one mode, but fails for another criterion at another corner.

“This is not just MCMM analysis but optimisation too, because it’s often the case of the worst-case timing for the circuit and the worst-case power of the circuit are in different process corners,” said Hasson, “so we do both analyses concurrently to get a netlist based on all of [the criteria] at the same time.”

Hasson says that about half of the claimed leakage reduction is due to the area reduction. The other half is due to a change of the strategy used to meet timing. To date, this has largely been done by “greedy” algorithms that substitute fast, but leaky, cells into critical paths to meet timing, and then try to recover the excess leakage by substituting some of the cells back out again. In the new approach, the major overhaul is to substitute in the fast-but-leaky cells as a very last resort to meet timing, so that there are fewer leaky cells to swap out.

“Leaky cells are a very, very expensive resource and can only be used as a last resort,” he said.

DC Explorer, the design exploration tool that use fast synthesis strategies to give developers a quick view of the likely characteristics and floorplan of their chip, also gets a revamp in this release with the addition of congestion detection based on the input RTL.

“Identifying congestion at this level, rather than at the place and route stage, can be very significant,” said Hasson, since it enables designers to reconsider the way they have coded their design early on.

DC Explorer and DC Graphical also get new RTL analysis and cross-probing capabilities in the latest release.

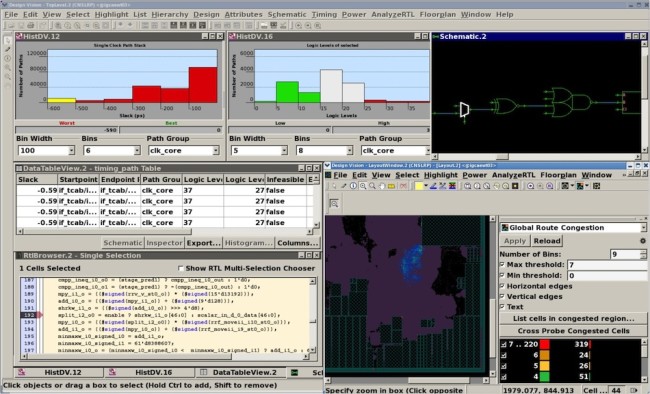

Figure 1 Synopsys' Design Compiler 2013.12 release enables cross-probing between multiple views of the design data, for faster debug

One of the new RTL analysis capabilities is the ability to see on a histogram how many levels of logic there are on each path of a design, and how they are distributed. This enables designers to, for example, track down paths that have a reasonable number of levels of logic for the technology and target clock but which still aren’t meeting timing. Clicking on the path can take you to a floorplan view that may reveal, for example, that because of the placement of macro blocks, one part of the path is too long. Another analysis might reveal a path with too many levels of logic, and then enable the designer to find the RTL that needs rewriting to avoid so many levels of logic.

“It’s a powerful facility that can speed up debug significantly,” said Hasson. Timing, levels of logic, the layout, and the RTL can all be cross-probed, so “you’ve got a way in from wherever you found the problem to whatever you want to look at to fix the problem.”

The 2013.12 release also improves the way the tools handle power intent. UPF is now supported in DC Explorer, so that designers can spec their power domains and the legal states for those domains and the tool will take them into account as it builds its first draft of the chip’s floorplan. The second update is support for the user’s ‘Golden UPF’ file throughout the design flow. Previously, each stage of the flow would take in a UPF file and write out a refined version of it to the next stage. In the latest release, the Golden UPF file is maintained throughout the flow, but augmented with additional information held in another file.

Further information

To find out more about the 2013.12 release, click here.