Managing waivers in reliability verification

Reliability verification solutions provide rules that help designers find and debug issues such as electrostatic discharge (ESD), multi-power domain crossing checks, voltage-aware design rule checking (DRC), latch-up, and company-defined best practices. However, while debugging error results, a designer or ESD engineer may encounter conditions that justify waiving certain violations. For example:

- A chip uses a new ESD protection scheme, but contains embedded intellectual property (IP) that employs an older ESD protection structure. The IP fails the checks for the new ESD scheme, but the results can be waived because this IP has always produced good chips in the past.

- A design block is verified before the full chip is assembled. The block may return certain electrical rule checking (ERC) errors because it does not yet have paths to signals in the context of a full chip. These errors can be waived during the block verification.

- A rule enforces a conservative design guideline. The errors that result from checking this rule can be waived if they are reviewed by the designer and/or the foundry, and deemed safe in the context of this specific design.

For maximum efficiency, advanced reliability verification solutions should include an automated waiver management functionality that can be used to resolve such issues quickly and easily. Of course, any solution must ensure that waivers are only applied to results that are legitimate errors. Waivers should never be allowed to mask the numerous ‘false’ results produced by non-optimized reliability rule checks.

Topology waivers for reliability verification

Reliability rule checking should run the same way, regardless of whether or not a waiver flow is enabled. The reliability verification solution should generate the same set of topological results, with the only difference being the categorization of the results. If the waiver flow is disabled, then all of the topological results should be output to the report file as violations. If the waiver flow is enabled, the reliability verification process should first apply the waivers to the topological results, and then transform the original results into a new (potentially smaller) set of non-waived results and a set of waived results, according to the outcome of its analysis. The reliability verification process can then output the new sets to the report file as violations and waived results.

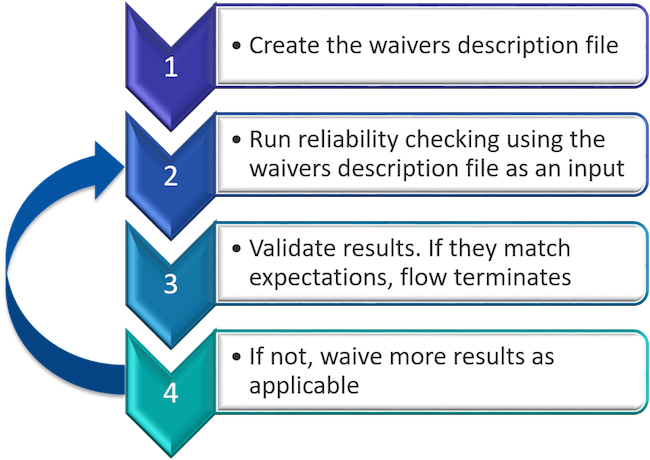

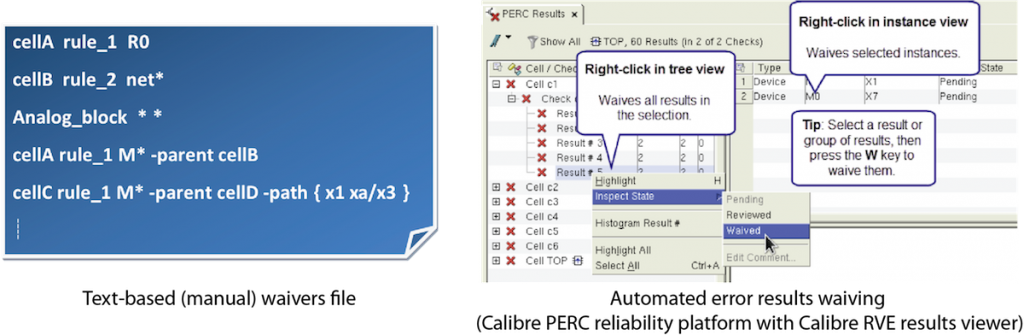

A complete waivers solution for reliability verification must support waivers at both the IP and full-chip levels. The waiver criteria are typically maintained in a separate waivers description file, which can usually be created either manually or by an automated process (Figure 1).

Figure 1. Waivers can be defined manually in a text-based file, or through automated selection (Mentor – click to enlarge)

After creating the waivers description file, the user runs the waiver process using the waivers description file as an input (Figure 2). After the run completes, the user validates the results. If the results are as expected, the process is complete. If not, the user must identify additional errors that should be waived, update the waivers description file, and re-run the process.

Geometric waivers

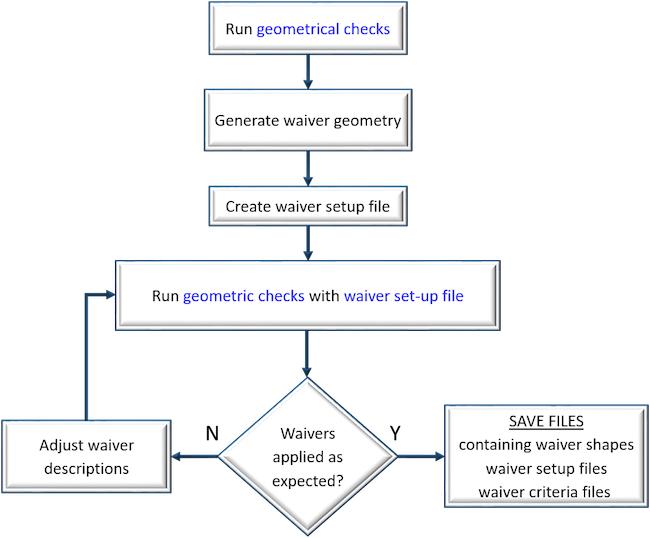

Some electrical reliability checks include geometrical results, so a complete waivers process must also be able to apply waivers for reliability rules that combine topological and geometrical information. This functionality allows users to generate and manage foundry-approved waivers for these rules. Such waivers must also be managed properly in the results output so their data can be preserved for analysis and validation. Figure 3 illustrates the flow.

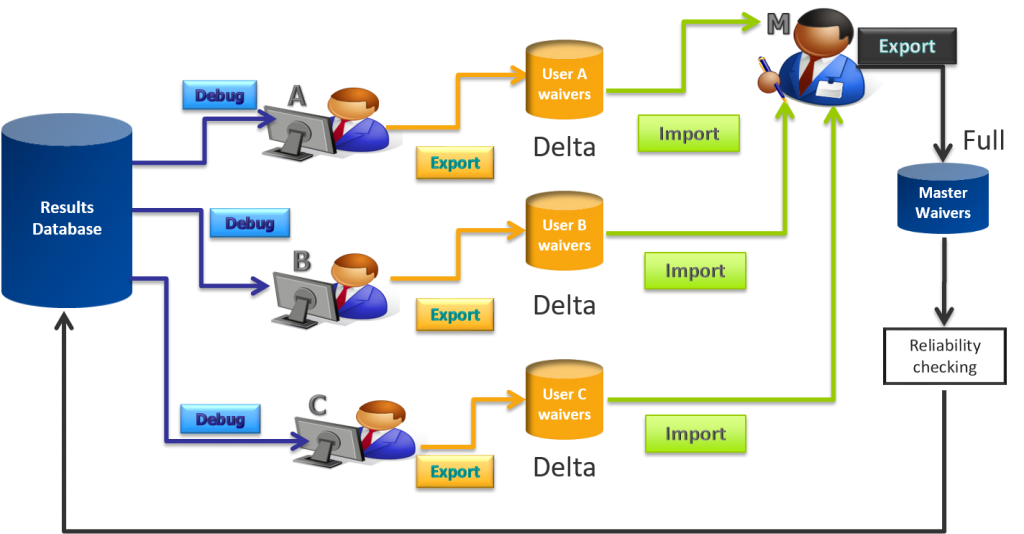

Multi-user waiver flow

Some reliability solutions support a multi-user waiver flow enabling multiple users to waive results in the same results database directory. While different waiver solutions may vary in the details, each user typically generates an individual set of waiver annotations in a separate waiver file. All of these individual waiver files are then imported and merged to produce a final set of results waivers that are applied during a waivers run. The multi-user flow is shown in Figure 4. Multi-user waiver capability helps teams complete reliability verification faster and more efficiently, as each user can concentrate on a specific set of waivers.

Summary

Reliability verification is an essential part of an advanced verification flow. Reliability waivers functionality gives users a methodology to mark reliability rule violations that can be safely ignored for a variety of reasons. Advanced waivers processing supports a full range of waivers needs, including automated waiver processing, the ability to waive both topological and geometrical violations, and a controlled methodology for multi-user environments. While waivers can be an important part of an efficient reliability verification flow, they must be applied and processed accurately to ensure that the integrity of the layout is maintained and that all potential reliability impacts are properly addressed.

Dina Medhat is a Technical Lead for Calibre Design Solutions at Mentor, a Siemens Business. She has held a variety of product and technical marketing roles at the company, and received her BS and MS degrees from Ain Shames University in Cairo, Egypt. She is currently a PhD student at Ain Shames University.

Dina Medhat is a Technical Lead for Calibre Design Solutions at Mentor, a Siemens Business. She has held a variety of product and technical marketing roles at the company, and received her BS and MS degrees from Ain Shames University in Cairo, Egypt. She is currently a PhD student at Ain Shames University.