How Ambarella met the demands of automotive DFT

Even experienced computer-vision companies face significant design-for-test (DFT) challenges when targeting the automotive market.

Ambarella has a track record that runs through solid-state camcorders, action cameras like the GoPro and broadcast TV. It brings two decades of experience to its work but still needed to add new tools and techniques to its DFT strategy for its CV22FS and CV2FS automotive camera SoCs. The devices leverage the company’s CVflow AI processing technology for use in forward-facing monocular and stereovision ADAS cameras, as well as computer vision ECUs for L2+ and higher levels of autonomy.

As ever, a major challenge was making sure the designs met the appropriate ASIL-B safety integrity level within the ISO 26262 functional safety standard. The company’s DFT flow therefore pulled upon emerging techniques such as in-line device monitoring. This involves distributing embedded monitors throughout each semiconductor device, with all of them connected through a common infrastructure to enable the rapid detection and reporting of random failures anywhere in the system.

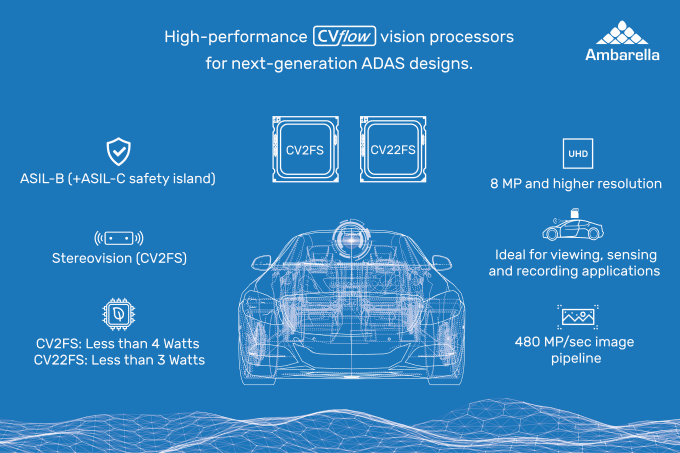

Figure 1. The ASIL-B-compliant CV2FS and CV22FS chips are designed for high-performance ADAS automotive devices with onboard computer vision (Ambarella)

To deploy this and other innovative approaches for its automotive SoCs, the company drew upon the Tessent test family from Mentor, a Siemens business. Some of the main elements used were:

- Tessent LogicBIST software: a built-in self-test solution for digital logic components with features optimized for nanometer SoC designs.

- Tessent MemoryBIST platform: a comprehensive automation flow including design rule checking, test planning, integration, and verification at either the RTL or gate level.

- The Tessent MissionMode product: a combination of automation and on-chip IP for the test and diagnosis of chips throughout an automotive electronics system at any point during a vehicle’s functional operation.

As a company developing multiple SoCs for different parts of the automotive market, Ambarella also says that breadth within its DFT platform was key. “Because Mentor’s Tessent ecosystem is highly scalable, it provides optimal flexibility for developing alternative designs and next-generation devices,” said Praveen Jaini, director of VLSI for Ambarella.

A dedicated page reviewing the range of capabilities in Tessent for automotive design can be found here.