Analog blocks go digital for faster integration

Startup Movellus aims to harness R&D in digitizing fundamental analog functions to make it easier to bring nanometer-technology SoCs to market. The company has launched the first of a series of IP-creation tools with one that will build all-digital phase-locked loops (ADPLLs) and integrate them into a design.

Movellus president and CEO Muhammad Faisal said: “We have been in R&D and private development for the last few years. We are hardcore analog designers. I’ve been a mixed-signal analog designer at Intel, PMC Sierra – so we bring those pain perspectives into this.”

The key problem Movellus wants to address is the delaying effect that custom analog design has on SoCs built on nanometer technologies. “They are very challenging and expensive to implement. If you look at 7nm or 10nm design, this has become the bottleneck,” Faisal said, with result that productivity has taken a major hit.

“They are dealing with that by developing the analog portions one or two years ahead of schedule. Analog is using iterations; digital is done using automation,” Faisal added. “There has been significant progress in EDA towards improving the analog-design experience but they have not been able to address the problem.

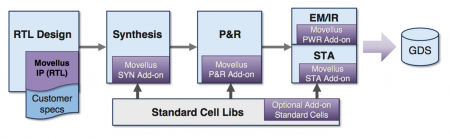

Image Addons provide support for the Movellus IP generators in a digital flow

“Digital tools have advanced significantly. And huge progress has been made by people in digital architectures and digitally assisted analog. An approach that has been successful in general is digitizing analog signals as soon as possible. But when you buy analog IP you are still stuck with the integration burden.”

By moving all the key blocks inside a function such as a PLL to digital implementations, Movellus aims to harness the rapid turnaround times possible with conventional EDA tools. Rather than deliver fixed IP cores, the company ships generators and a number of addons that plug into synthesis and place-and-route tools. The current early-access customers are on Cadence flows but the company is porting the addons to work with Synopsys.

“Once the customer has installed our addon software, the entire flow looks exactly the same as a digital flow. The addons allow the existing tools to handle the need to use feedback loops at the transistor and the dynamic range needed to tune across PVT corners,” Faisal explained.

“There are optional standard cells, though we can do it with existing standard-cell libraries. Long-term our goal is integrate those additional cells with the standard-cell libraries from the foundries – that could be additional revenue for them.”

The additional standard cells implement low-level functions that are useful for situations such as tuning circuitry across a large dynamic range. One cell is a tristate inverter that is not often offered in conventional digital libraries, though some IDMs have made use of them. “They are not normally there because the standard tools do not understand them. But we can use them to change drive strength and tune it.”

With support from downstream addons and no need for specialized components such as large MiM capacitors or inductors, the IP is generated as standard RTL. Faisal said. “We can generate the IP in a matter of hours. I have never seen analog implemented for PLLs in less than 12 man-months.”

There are tradeoffs in terms of design time and core efficiency. One PLL implemented within a month for a customer working on IoT designs had a power consumption of 700nW and a jitter of 200ps. Older projects saw jitter reduced to single picoseconds with design times of up to three months and a power consumption measured in milliwatts. A more recent project that has recently taped out saw the IP generated in just two hours, offering a jitter of less than 50ps with a power consumption of 0.5mW.

Early customer Mythic, which is developing processors for artificial intelligence applications, was able to tweak the IP and avoid missing tape-out deadlines. Mythic CTO David Fick said: “Their generator allowed us to focus on designing our SoC without worrying about any schedule slips due to late manual analog customizations needed to meet our goals. For example, when we needed to push a metal stack change, Movellus was able to provide a correct IP in a matter of hours.”

Movellus aims to follow its initial launch of a PLL generation and integration suite with DLL and low-drop regulator (LDO) tools. “We have PLL, DLL and LDO generators. But work has been done to expand into other domains, with ADCs, DACs, and RF. There is already significant activity in all-digital circuits for radios. We know that a lot of the technologies we have developed are extensible to those applications,” Faisal said.