Performance and timeout checks added to on-chip network

Sonics has add static performance analysis to its SonicsStudio tool for on-chip network creation as well as a timeout capability for its SonicsGN network intended to prevent non-responsive cores from crippling an SoC.

“Our aim is to provide real-time input back to designers so they can optimize the design of their network,” said Drew Wingard, Sonics CTO.

Although simulation will remain a key part of evaluating the suitability of an NoC for target applications, Wingard said static analysis can provide faster feedback on whether a given configuration stands a chance of meeting the proposed demand. For example, the analysis may show that a particular link between cores is undersized and likely to present a bottleneck. On the other hand, a control-oriented part of the network may be shown to be over-provisioned.

“What we’ve done here is recognize that from an abstract description of use-cases you can do a lot of this work without simulation,” Wingard claimed.

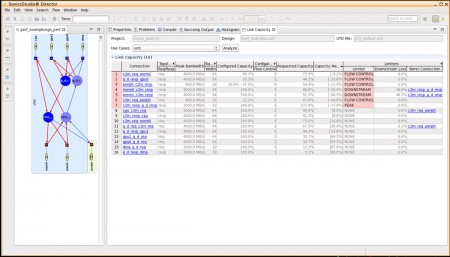

Image Static performance analysis in SonicsStudio

In the tool, architects describe the system use-case scenarios by entering throughput characteristics and requirements in a structured table or by extracting that information from simulation stimulus that may already exist for that use-case.

For the timeout detection added to SonicsGN, Wingard said the company managed to come up with a scheme that allows the system to recognise that a core has failed to respond to a request before the inactivity locks up the system or causes an application to fail.

Wingard said the facility is useful for debug and silicon bring-up as early driver and application code or bugs in the hardware itself can often lead to IP cores moving into an unsupported state and then becoming unresponsive, often causing the system to freeze.

To avoid the situation where the hang prevents access to the control registers by the device that initiated the stalled request, the data stored by the timeout protection logic can be accessed using a control bus. A key focus for the SonicsGN timeout detection is power consumption, Wingard said.

“We’ve had timeout detection in prior generation products. We are really concerned in a product like SonicsGN about power. For timeout detection you need counters and on a network like those supported by SonicsGN you will have a lot of ports. You don’t want 200-plus counters running all the time.

“So we don’t necessarily count individual cycles. Instead we distribute from a central location a set of time base signals that wiggle every n clocks. We send out four signals, each one four time slower than the prior one. Agents subscribe to one of those timebase signals and use them to determine how long a transaction has been outstanding. You sacrifice a small loss of precision,” Wingard explained.