Synopsys launches single kit to optimize IP across PPA

One of the key challenges in SoC design is cross-optimizing for power, performance and area (PPA) across the different types of cores within the design. Synopsys has launched the DesignWare HPC (High Performance Core) Design Kit to achieve just that.

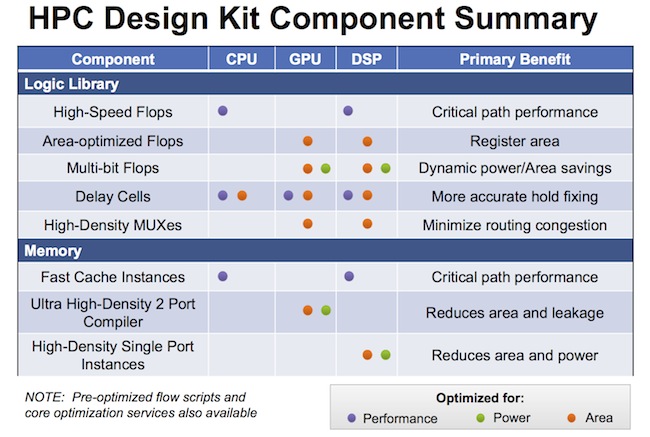

Available from July, the kit focuses on balancing the requirements for CPU, GPU and DSP cores and has been developed both for the company’s own IP and that of partners including Imagination Technologies, CEVA and VeriSilicon. The kit also includes an ultra high-density memory compiler.

Overall, Synopsys is saying that the kit can deliver a 10% increase in performance, 10% reduction in area and 25% reduction in power, though these will obviously vary depending on the application. A specific case study optimization for an Imagination PowerVR Series 6 GPU gave improvements of 10% in area, 20% in leakage power and 25% in dynamic power.

This graphic summarizes some of the various implementation knobs within the new kit.

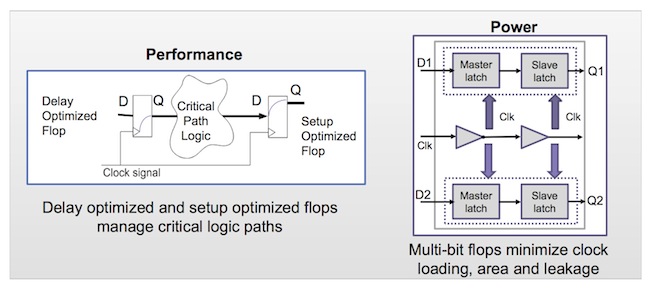

One interesting element here is the inclusion of multi-bit flip flops. These have been used for optimization before but are primarily implemented on a custom basis, so they have taken time to realize. The new kit automates that.

The flops are especially useful because they help save area by sharing circuitry and reduce the load on the clock tree signal. For best effect, they are best used in 4 and 8bit combinations, though 2bit is also possible (the technique will scale to 16bit but for most designs the extra returns for going that far are negligible).

The kit also features delay- and setup-optimized flops for use on critical logic paths.

Overall, the kit features more than 125 new standard cells and memory instances. You can optimize cores individually or, more likely with this launch, across different blocks.

And the reduction in turnaround time? Synopsys is claiming 25% with multiple core implementation possible within 4-6 weeks for a typical target design that uses its FastOpt design services.

At launch, the kit is optimized itself for use on TSMC’s 28nm HPM process. Synopsys has also published a white paper on optimization across multiple types of core.