Cadence moves into safer design with Virtuoso changes

Cadence Design Systems has made additions to its Virtuoso mixed-signal design environment intended to improve design for manufacture and the ability of teams to create and test safety-critical systems.

The company has developed three tools that fit into the Virtuoso environment – the ADE Verifier, Explorer, and Assembler. They are designed to provide an easier way for those using traditional mixed-signal verification flows to feed their results into the VManager tool that SoC teams may be using to coordinate overall verification for projects that need compliance with standards such as ISO 26262 for automotive or IEC 60601 and 62304 for medical devices.

As traceability is a requirement for these types of safety standards, the ability to tie requirements to specific verification runs and tests from a high level is vital. Although VManager can provide the traceability, Cadence product marketing director Steve Lewis said the company wanted to come up with a way of incorporating analog verification without forcing team members to be retrained on unfamiliar tools and modelling techniques.

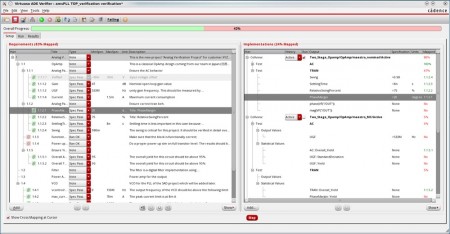

Image The ADE Verifier maps analog simulation results into VManager

“That traceability has been in the digital world for a long time but it’s been missing in many cases on the analog side,” Lewis explained. “It was time for us to offer a tool that was well integrated into the Virtuoso world. It will allow them to answer the questions: ‘What is the status of the analog design?’ and ‘Did we cover all of the specification?’.”

Two of the tools work at different levels of abstraction. The Explorer is aimed at circuit-level designers and pulls in features from the existing ADE XL tools to support variation-aware simulation across multiple corners. This level of simulation can support the need to show that the analog circuitry will work under all conditions specified in the requirements or mission-plan documents.

The Assembler is aimed at engineers working at the block or SoC level who need to determine the block’s ability to meet the design-for-manufacturing requirements. An additional package of variation-aware support is available for this to handle the additional complexity of finFET-based processes.

A third tool, the ADE Verifier performs the job of automatically mapping the results from the other tools across to VManager to support requirements analysis at the SoC assembly level.

“Some users said ‘we jumped the divide already and for us these worlds are not so separate anymore’. If a test is shown as failing in VManager, the designer may see it there and want to go into the analog tools to see what is going on. We don’t have that level of integration today but we are working with customers to see how that interaction should work,” Lewis said.

As well as the additional tools, Cadence has reworked the rendering and display engines inside Virtuoso to speed up drawing operations. The redesign takes advantages of improvements in display processors as well as algorithms to prune data intelligently before the rendering step to reduce the amount of work needed to pan across a circuit or zoom into it.

Changes have also been made to modgens to make it easier to tweak the shape on the fly to suit a particular task – such as altering dummy features at each end of a collection of transistor fingers.