Synopsys begins IC Compiler II roll-out

Synopsys has added a second string to its IC implementation bow with the launch of IC Compiler II, a next-generation tool intended to address the most difficult place and route tasks on designs with up to 500 million instances.

IC Compiler II is the result of a three-year research effort at Synopsys to re-engineer its place and route offering for greater effectiveness on large designs. It will be offered alongside IC Compiler, whose development will continue.

According to Saleem Haider, senior director marketing at Synopsys, the development of IC Compiler II was a speculative venture to explore the possibilities of a new approach to place and route.

“Three years ago we looked at IC Compiler and said ‘We’re going to go on doing that, but what more can we do? What if we build a new system from scratch? Can we then get a tenfold improvement in productivity?

“The new effort is all about being more global in scope: everything is up for consideration,” he added.

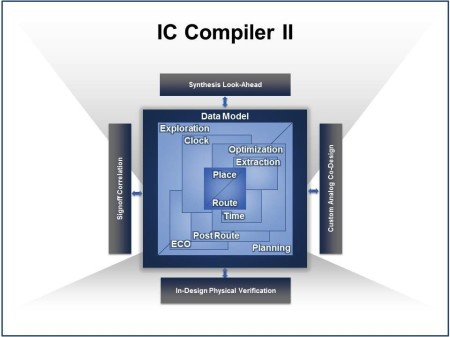

Figure 1 IC Compiler II binds together old and new to tackle the largest IC designs (Source: Synopsys)

Synopsys has applied a ‘rebuild, rethink and reuse’ strategy to the development of IC Compiler II.

Data model

One of the most important parts of this is a new data model.

“When we started we knew certain bits of the system had to be rebuilt and a new infrastructure was a big part of it,” said Haider, arguing that the data model is a key determinant of how fast data can be passed to and from the various engines that act upon it, and therefore of overall performance.

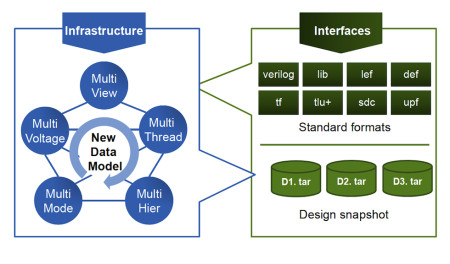

Figure 2 A hierarchical, multithreaded data model underpins IC Compiler II (Source: Synopsys)

The new data model is inherently multithreaded, so it can make efficient use of the available hardware, and supports both flat and hierarchical design styles. It also supports multicorner, multimode analysis and various standard data formats.

Having rebuilt the basic infrastructure, Synopsys was then able to rethink how the various key engines in the tool, such as timing, extraction, clocking and optimization, were implemented.

Alongside the rethought elements of IC Complier II, Synopsys has also reused two critical engines: the conjugate-gradient placer and the Z router.

Performance

Synopsys’s claim for IC Compiler II, along with its enhanced capacity, is a potential tenfold improvement in design throughput. This is achieved by making the design-planning process ten times faster and five times more memory efficient, and the implementation process five times faster and twice as memory efficient. Synopsys argues that an average fivefold faster runtime and an average halving of memory usage adds up to an average tenfold increase in throughput.

Better performance should enable designers to evaluate many floor-planning alternatives quickly, to arrive at the right starting point for implementation.

According to Haider, the partial design-planning process has got faster in part because of the new infrastructure and in part because the algorithms have been reworked. The full design-planning step offers a tenfold speed up which enables ten times more exploration of the design.

For a 20 million instance design, Haider said, planning would be done on the whole design at once while implementation might be done on partitions of 2 or 3 million cells. With IC Compiler, the implementation of that partition might take five days, which would be reduced to a single day with IC Compiler II.

“If the implementation is done in a day instead of a week, you may finish your chips earlier or you may use the speed-up to do more exploration and therefore get a better design and a higher quality layout,” said Haider. The speed-up could also enable you to use fewer engineers on that part of the design, or fewer partitions.

“With the real-time speed-up, customers can take, for example, three partitions and put them into one, which then gives the optimiser more room to roam: you can just let the optimiser rip,” said Haider.

Optimisation

IC Compiler II includes a new global optimisation strategy, based on a new way of modeling the design known as APS.

According to Haider, APS offers a different way to analyse a global view of the design than the current state of the art, which looks at the critical parts of a design with a critical local view, applies transforms to critical logic, times their impact, and then checks progress towards a given goal. APS analyses globally, and tries to optimise globally.

“The incremental, local part doesn’t go away,” he added. “We always have the ability to locate the problem area in the final closing stages, post route, and that is what we will do to optimise on the local scale.”

What-if routing

IC Compiler II includes enhancements that are meant to get to better results more quickly. For example, the current approach to finalising a design involves looking for timing violations, deciding on a way to transform the logic that has caused the violation, and then rerouting that bit of the design to see if the transforms and new routing solves the timing issue.

In IC Compiler II, according to Haider, the optimiser can query the router and say “If I change the logic in this way, what with the outcome look like?”, getting an early sense of whether a particular transformation will overcome an issue.

Multicorner, multi-mode support

IC designs undertaken on emerging node processes have to work properly in many operating modes and at many design corners. IC Compiler II has been developed to work with multicorner, multimode (MCMM) designs efficiently.

“MCMM in IC Compiler II was a key consideration from day one and one of the parts that was very difficult,” said Haider.

The original IC Compiler handles MCMM designs using the concept of ‘scenarios’, which represent both an operating mode and a design corner (and which are also used in Prime Time). With this approach, according to Haider, complex designs can generate a lot of scenarios, which then have to be aggregated to make it possible to do the physical implementation during place and route.

“And we have got very good at working out which of those scenarios really matter,” said Haider.

IC Compiler II overcomes the issue of managing a rapidly growing set of scenarios by storing modes and corners separately, rather than embedded within scenarios. This makes it easier to simplify the placement and routing task by superposing the constraints imposed by each mode and corner.

Working at the mode and corner level of abstraction eases factorization, reducing the constraints and the representations, which in turn reduces the analysis effort required, loading times and so on.

“This means that, for example, we can go from six modes and corners to 18 modes and corners and the memory and the runtime [to process the design] don’t explode,” said Haider.

Progress and availability

IC Compiler II is a work in progress. According to Haider, the preroute part of the system has been finalised, including placement, clock-tree synthesis and optimization.

The post-route part of the tool is still in R&D but is due to be finalized in time for first production shipments ‘midyear’. Broad shipments are planned for the year end.

Further information

There’s much more on IC Compiler II here.