RC extraction from ‘virtual fab’ models may speed PDK availability

Coventor has updated its SEMulator3D virtual fabrication tool so it can extract predicted resistance and capacitance values from its models. The analysis tool could be used to speed up the availability of early PDKs for rapidly evolving processes.

SEMulator3D abstracts IC manufacturing steps into behavioural models, so that it can simulate a a whole process in a ‘virtual fab’. Because the process steps are modeled using behavioural abstractions, rather than full physics, it becomes practical to run multiple options to explore how variations in each step will affect overall outcomes.

According to David Fried, CTO – semiconductor at Coventor, this approach means the company’s 3D structural models are “exceptional at predicting the process of the fab.”

The add-on tool, SEMulator3D Electrical Analysis, derives R and C values from the SEMulator3D models.

“A lot of TCAD solutions idealise geometry,” said Fried, “for example, by modeling a via as a simple cylinder. They can sometimes work with limited geometries, and be slow. We have developed a solver technology to make the analysis fast and to do it over relatively large structures.”

Fried says Semulator3D is already in use at IDMs, foundries, memory makers, CMOS imaging specialist and more, where it is used to help with process development.

“Foundries need to deliver a process technology to the fab and a PDK to designers. If we have a better way to predict RC, we can improve the quality of PDKs earlier,” he added. “If we can get the accuracy level higher, earlier, it reduces the amount of [as the process develops] and so reduce the decelopment time. I’d like to see this kind of information being used in parasitics and parameters in early PDKs.”

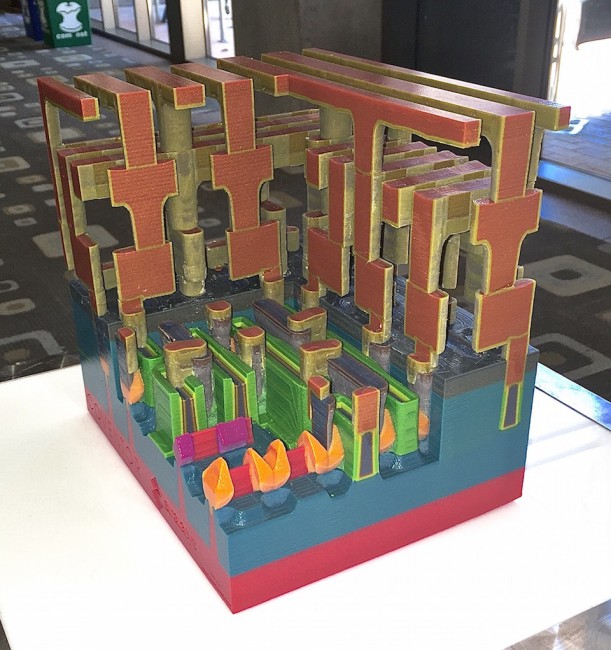

Figure 1 Model of a generic 14nm finFET process, 3D printed from a SEMUlator3D 'virtual fab' model

David Fried won the Grand Prize in the 2016 DAC Silicon/Technology Art Show, with this 3D-printed model of a 14nm finFET process, derived from a SEMulator3D model. The model was developed from information in conference papers and other public sources, and then translated into a data format suitable for 3D printing. The model was then printed in a single run on a StrataSys printer, and used dithering to derive 27 material colours from three source material colours.