January 12, 2022

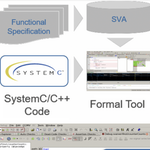

Automated formal technologies can be used to ease the debug and functional verification burden of SystemC/C++ code prior to high-level synthesis. This tutorial, first presented at DVCon Europe explores how these formal techniques can be deployed and provides real-world examples.

February 25, 2011

The article is abstracted from a presentation given at NASCUG by Umesh Sisodia and originally developed by Ashwani Singh of CircuitSutra Technologies on how to create adaptors between various modeling abstraction levels in SystemC.

December 14, 2010

This paper describes Medea, a NoC-based framework that uses a hybrid shared-memory/message-passing approach. It has been modeled in a fast, cycle-accurate SystemC implementation enabling rapid system exploration while varying several parameters such as the number and type of cores, cache size and policy, and specific NoC features. Also, each SystemC block has its RTL counterpart [...]

September 10, 2010

Simulation speed is a key issue for the virtual prototyping (VP) of multiprocessor system-on-chips (MPSoCs). The SystemC transaction level modeling (TLM) 2.0 scheme accelerates simulation by using interface method calls (IMC) to implement communication between hardware components. Acceleration can also be achieved using parallel simulation. Multicore workstations are moving into the computing mainstream, and symmetric [...]

April 14, 2010

One year after the publication of a draft, the analog and mixed-signal (AMS) extensions to SystemC AMS will be issued as a standard at the Design Automation and Test in Europe conference in Dresden in March 2010. At this point, SystemC/SystemC AMS will become the first ESL technology to cover continuous time modeling as well [...]

December 1, 2009

The verification, test and debug of SystemC models can be undertaken at an early stage in the design process. To support these techniques, the SystemC Verification Library uses a concept called data introspection. It lets a library routine extract information from SystemC compound types, or a user-specified composite that is derived from a SystemC type. […]

June 1, 2009

The article describes a methodology that bridges the gap between SystemC transaction-level models (TLMs) that are used for architectural exploration and SystemC cycle-accurate models of hardware that typically follow much later in a design flow, after many sensitive decisions have been made. The behavior of the cycle-accurate models can be verified in the complete system […]