Emulation strategies for SSD verification

SSD controllers are becoming increasingly complex and as a result emulation is now the first choice for SSD verification. But your strategy must still meet five key criteria.

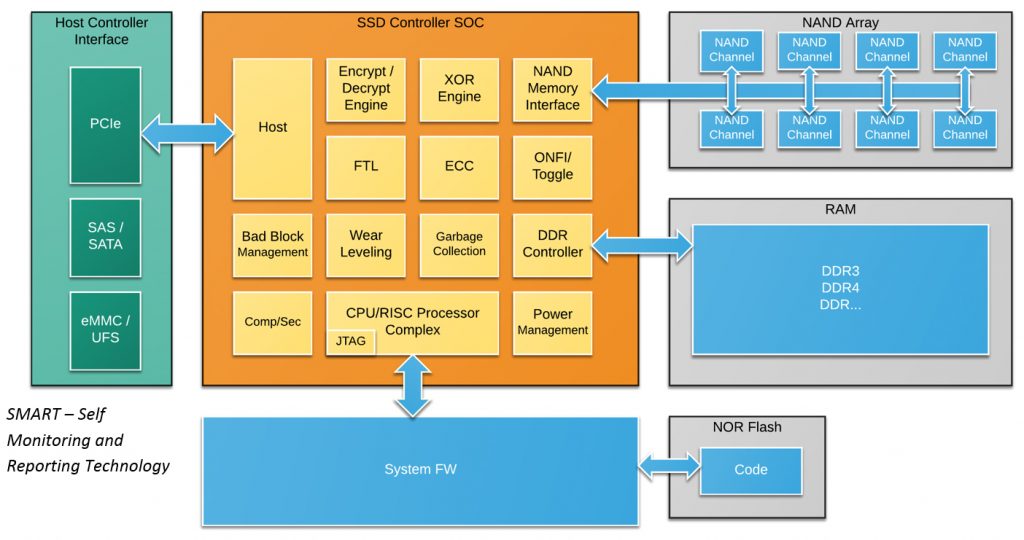

A solid-state drive (SSD) controller is a complex embedded system comprising multiple hardware blocks that are typically connected to one or more processor cores, with controller firmware and application software providing key product differentiation. In addition, an SSD operates with a host protocol interface connection, of which there are several types, such as SAS, SATA, PCIe, and NVMe. Finally, there is a flash channel communicating with a NAND array — which provides high-density, non-volatile memory storage for the SSD — and a DRAM connection for user data (Figure 1).

Given the design sizes, complexity, and long execution runtimes needed, as well as the high reliance on processors and software in a modern SSD controller, it is no surprise that the tool of choice for many engineers undertaking SSD verification is a hardware emulator.

However even for emulation, it is not easy to handle the number of tasks required, but we can manage the task by breaking it down into five must-have capabilities for any SSD verification project.

The five must-have capabilities for SSD verification

1. Multiple host-protocol interface solutions

It seems obvious to state that an SSD verification solution should have host interface applications for SATA, SAS, PCIe, and NVMe — to name the most popular protocols. What is not always appreciated is that traditional in-circuit emulation (ICE), which uses external hardware attached to the emulated SoC, can be very troublesome to debug because of the random behaviour of hardware. A solution based on Mentor Graphics emulation family handles this extremely well thanks to the recently-launched Veloce Deterministic ICE App. It delivers repeatable results to make the debug task significantly easier and less time consuming.

2. Memory solutions

Other obvious requirements for SSD verification are the NAND flash array and DRAM models that form part of DUT emulation. Today, getting good models is becoming increasingly challenging as memory capacities reach into the terabytes and beyond. Models need to use capacity efficiently, have the flexibility to be configured for verification, be easy to use, and, finally, deliver the performance required for emulation. The Mentor answers to this challenge are the Veloce FlexMem memories which allow for the creation of huge memories that can be compiled and synthesised into fully-associative, cache-based implementations on Veloce hardware. These can then be seamlessly accessed from both software and hardware.

3. Hardware-software integration

As noted, SSD controllers come with a great deal of firmware and software that must be debugged in conjunction with the rest of the hardware. You need software-hardware tools that support debug using fully synchronized and easily viewed data across the two domains, including logic simulation waveforms, processor states, source code, internal memory, registers, stacks, and output.

Mentor’s Codelink is one of the leading solutions to this challenge. It works in much the same way as the latest generation of digital video recorders (DVRs). During functional simulation or emulation, Codelink’s advanced tracing technology automatically captures and compresses all important activity inside a design’s processors. Verification engineers can then ‘playback’ the simulation or emulation run with features such as fast forward, rewind, replay, pause, slow motion, zoom-in, single step, and pan. Complex failures can be diagnosed within a single, multi-view debug environment. The alternative involves extensive analysis of multiple files and databases. Offloading the debug sessions from the emulator significantly boosts productivity compared to traditional JTAG techniques, and frees the emulator for other users.

4. Low power demands

There can be tens of thousands of SSD drives in a datacenter. It is critical to keep the SoC power consumption as low as possible because the related cooling costs can become enormous. So it follows that low power is a truly significant metric for SSD controllers.

Low-power analysis tools must support both RTL and gate-level power estimation and provide average power, peak-power, and hot-spot analysis. They also should be seamlessly integrated with other verification tools, and be capable of very high runtime performance because of the size and complexity of these designs.

To meet these requirements, Mentor created the Veloce Power App. It represents a fundamental shift in the way power measurements are done that addresses the new requirements brought about by the massive changes to how consumers are using high technology

This approach provides a fast, clean, and highly effective method of quickly and thoroughly estimating power consumption in modern SoCss. It eliminates the core problems affecting testbench-based approaches currently used by simulators and emulators by supporting accurate, timely, and efficient power analysis at the system, RTL, and gate level. It accomplishes this by measuring power in a targeted application environment while running actual software applications — just what is needed for a low-power SSD solution.

5. Performance metrics

Given all the hardware and software in an SSD, engineers need to understand the performance, throughput, and response times for their SSD controllers. Customers will buy their products based on the metrics associated with those features. So it is very important that these kind of things can be measured and verified.

To that end, the emulator must be compatible with available performance analysis tools that run on the design. This allows designers to see what the actual IO operations are and get metrics on the IOPS, bandwidth, and latency for the SSD SoC.

Summary

The Veloce emulation family offers a new-generation of verification solutions for enterprise storage systems. It delivers the five must-have capabilities for SSD controller verification:

- High-Speed Verification Solutions for Multiple Host Protocols

- Optimised Memory Device Models

- Hardware/Software System-Level Debug

- Accelerated Low-Power Applications

- SSD System Performance Analysis

To learn more about the rise of SSD technology and Mentor’s emulation solutions for storage system designs, read the new whitepaper Veloce Delivers Best of ICE and Virtual Emulation to the SSD Storage Market.

About the author

Richard Pugh has 30 years of experience in electronic design automation, working in IP, ASIC, and SoC verification with positions in application engineering, product marketing, and business development at ViewLogic, Synopsys, and Mentor Graphics. He is currently the Product Marketing Manager for Mentor’s Emulation Division.

Richard holds an MSc in Computer Science and Electronics from University College London and an MBA from Macquarie Graduate School of Management, Sydney.