‘Even the software guys are starting to talk in milliwatts’

System-level power is the next frontier for a power-intent standard – or rather a collection of them – being developed by a partnership between Accellera, Si2 and the IEEE.

At the 2015 Design Automation Conference in San Francisco, Accellera, Si2 and the IEEE co-hosted a session looking at upcoming standards for system-level power as well as seeking input on how to proceed. The cooperation between the groups has been welcomed as many users and vendors are keen to avoid the split that occurred with the RTL power-intent standards CPF and UPF.

TSMC director Tom Quan reiterated the need for work on power at a higher level: “System-level design will enable the most efficient architecture. Power modeling early is the key.”

The question is how to get there. Although standards are still being thrashed out that will make easier to plug power models together, one of the key issues with system-level power analysis is encouraging engineers who are not involved with hardware design to become more involved. This is now happening, said Microsoft hardware design engineer Victoria Vishnyakov: “Our architects are optimising their system not just for performance but power performance. Even the software guys are starting to talk in milliwatts.”

Vishnyakov added: “Each one of these disciplines kind of work in parallel so each one does their own thing. The software guy starts working with power when they get the hardware but, with that, there is no real feedback to the hardware and by the time we have the hardware there is not much time to to change it. You are then very close to launch.

“The architects often work to highly simplified power models and benchmarks,” she noted. Without a good picture of the actual system operations, they cannot make optimized decisions. “We want an approach where multiple disciplines have visibility to each other.”

Power visibility

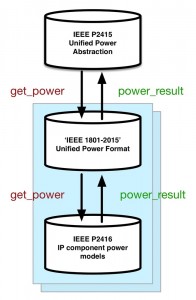

In principle, improved visibility through the architecture and design flow is what the combination of IEEE P2415 and IEEE P2416 and an overhaul of UPF/IEEE 1801 should enable. The result may be a situation where early power analysis is used to generate valid power domains and controls that can be assembled into an SoC design without having to stitch them together by hand using today’s somewhat manually intensive processes. Since UPF was developed, hardware engineers now have a clearer idea of how power domains are architected and used, which can drive better assumptions in the partitioning, synthesis, and layout tools. Conversely, those implementation subtleties have a major impact on the construction of the system-level power model.

Image Conceptual diagram of the relationship between the proposed IEEE standards

Consultant Barry Pangrle said: “The assumption behind ‘1801 was, ‘if I do this logical partitioning, power partitioning will follow’. It didn’t really work out that way.”

Ahmad Ansari, principal engineer at Xilinx, pointed out that an early assumption behind UPF’s structure has turned out to be false and therefore increased implementation complexity. For example, there are big differences between physical and functional dependencies when it comes to defining and controlling power supply rails. “You may have two blocks that coexist in one [power] island but which belong to logically separate subsystems,” he said.

If one subsystem needs to stay active, so does the other, even if it is performing no useful work and could otherwise be powered down. Conversely, Ansari said: “DDR memory control may belong to the applications processor unit but the memory may also be shared with the real-time processor. When the applications processor goes to sleep, you can’t take the DDR down because it’s shared with the real-time processor. Those functional dependencies need to be captured and defined in the power models.”

Increasing model availability

Low-power design consultant and Si2 director of system-level power Jerry Frenkil said: “We found that executing a power-aware flow is limited by model availability. This is an area that’s crying out for a standard. And specifically, there is a need for a standard for IP blocks.”

For its work on modelling standards, Si2 has adopted an approach based around the idea of power ‘contributors’ developed with Nagashyamala (Nagu) Dhanwada and David Hathaway of IBM together with North Carolina State University researchers Rhett Davis and Harun Demircioglu. Instead of using circuit-level models to compute tables that can be used in system-level simulations, contributor modeling treats the components of power consumption as separable elements.

Examples of power contributors include the channel and gate leakages of single transistors, the leakage through a given transistor stack and the charging of capacitance as the gate switches. A low-level power model combines those contributors to come up with a power estimate for a given cycle. In principle, these models can be made independent of power, voltage and temperature (PVT) variations. Although the PVT contributions themselves need to be factored in for a given process and library for a final, accurate model, the contributor approach allows the benchmarking of different circuit and algorithm strategies against each other.

“The contributor form can help you explore all the system level schemes,” said Dhanwada. “Abstraction is key to enabling power-aware system simulations. With the contributor approach we should be able to have a single framework for models that moves from spreadsheet models to full [simulation-based] models.”

Si2 has provided this modeling technique to the IEEE P2416 working group. “We see these standards groups as being recipients of the work that we do,” Frenkil said.

Abstraction support

The P2416 standard focuses on state-based power data and modeling, said Stan Krolikoski, Accellera secretary. IEEE P2415, on the other hand, is for providing power abstractions of assembled components and blocks to simulation tools.

Vojin Zirojnovic, P415 chair, said the standard would be used to define the chip’s power-related features such as clocks, power rails and other power controls and sequencers at a high level. These allow the testing of different power-control algorithms to see how the system-design performs under different loads and also sanity-check the sequences to ensure that a key block required for other functions is not turned off by mistake.

“If we can build a bridge into 2415 and abstract it for the software guys, that would be the vision.” said Vishnyakov.

Upcoming changes to UPF are also intended to provide a bridge to higher-level models. IEEE P1801 secretary Sushma Honnavara-Prasad said: “What we want to do is extend UPF up as far as possible.”

Some of the core elements for that, Honnavara-Prasad said, already exist. “We already had the concept and the commands are there: begin_power_model and end_power_model.”

To that infrastructure, the intention is to add commands that define legal power states and state transitions. These will be coupled to power functions that compute the consumption of each state based on a set of variables fed to algorithms implemented by EDA tools but which will not be defined in UPF itself. As a result, the future UPF would support higher-level modeling work, potentially taking data and specifications defined using IEEE P2415 models and feed those down into directives that implementation tools use to create power domains, sequencers as well as to support SoC verification.

Simulation scenarios

Pangrle described scenarios that system architects and designers could explore with an idealised workflow that could be enabled by the three standards. He took the example of a multicore design using different dynamic voltage and frequency scaling (DVFS) strategies. One strategy supplied the same voltage to each of the active processors, the other allowed the voltage for each to be different, which would incur a higher area overhead for the additional supply rails and voltage converters. Additionally, the power-management algorithms could be implemented in either software or hardware.

A transaction-based model would, using power models, evaluate each of the combinations and deliver a set of graphs that show power against time for each under different workloads, such as video decoding and web browsing.

Pangrle added: “Within this framework, I want to do high-level exploration, carve things up and decide what will run in each of the processors at these different voltages. Hopefully, the tools will be smart enough to figure out where the islands and level shifters need to go and then generate the UPF.”

Power models would also potentially show up subtle interactions, such as the situation with Big.Little-style architectures where, on paper, it makes sense to shut down a core and migrate its workload but where the energy cost of migrating the data stored in cache makes that a higher-energy option for certain workloads.

Although there is a lot of standardization effort to be completed across no less than three groups, momentum appears to be building for a better system-level power modeling environment that could feed all the way down into implementation tools.