How new RTL floorplanning techniques speed physical design

Advances in RTL floorplanning help cut front-to-back-end iterations, speed synthesis by 10X and boast the capacity needed for today’s designs.

RTL floorplanning is one of the most important steps in the design flow. It is key to achieving better quality of results and faster turn-around-time. A new generation of physical RTL synthesis and floorplanning tools can give design teams an advantage in getting production-ready results faster than ever before.*

Consider these three limitations facing RTL synthesis today.

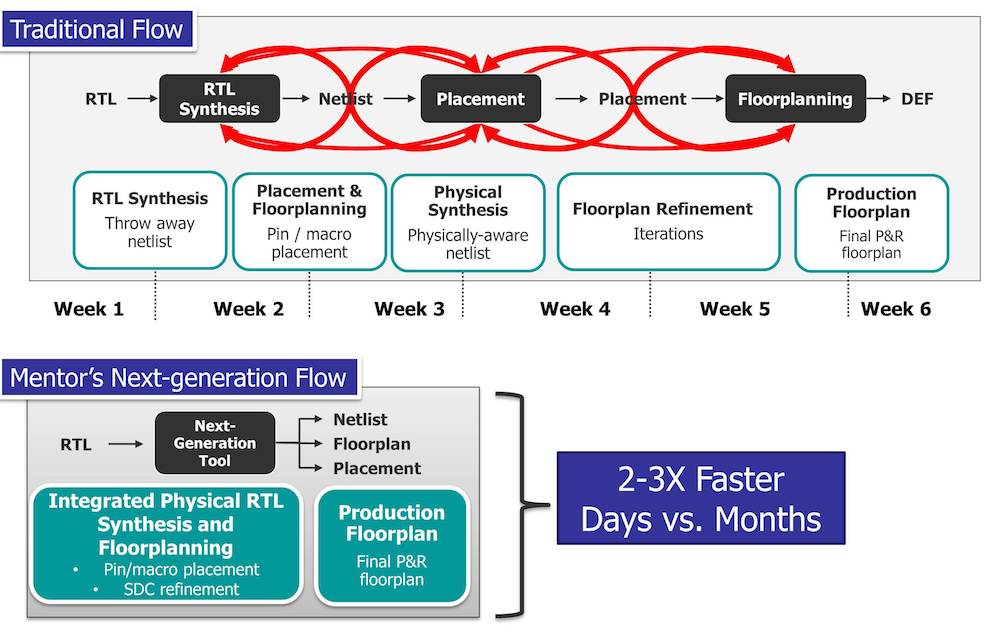

- Conventional physical synthesis flows lack full chip-level floorplanning capabilities and they perform synthesis with minimal physical information. This prolongs the iterations between front-end and back-end design teams (Figure 1 – click image to enlarge).

- Many RTL synthesis tools have limited capacity. Synthesis and RTL floorplanning on designs that are broken down into smaller blocks can suffer from poor quality pin placement, higher feed-through count, and over-constrained timing budgets.

- Finally, designers often run into congestion and timing problems at later stages of physical design because the synthesis tool uses inaccurate RC and physical models during synthesis.

Next-generation RTL floorplanning

Accurate and fast RTL-level floorplanning helps resolve these problems early in the design flow. Designers can use early floorplanning at the RTL level for RTL-level IP signoff, RTL prototyping floorplanning, and production quality floorplanning that can be used as the starting point during back-end implementation.

When addressing RTL-level IP sign-off, the IP developer may be someone with very little knowledge of physical design. He or she can use an RTL-level floorplanner to determine whether the IP can meet the performance, area and power targets during physical implementation.

For floorplanning RTL prototypes, designers can gauge the quality of the RTL from a physical implementation perspective without iterations with the back-end teams. This saves significant time.

Next-generation RTL-level floorplanning technologies, such as the Mentor Graphics Oasys-RTL synthesis and floorplanning tool (previously RealTime Designer), allow RTL designers to read in the entire design and then automatically create a floorplan based on the high-level RTL modules, macros, and design data flows. Once the initial floorplan is created, congestion, timing, power and area metrics can be analyzed to inform further incremental changes that fine-tune the floorplan.

Designers can use RTL synthesis and floorplanning tools that handle hard macros and custom blocks so that such features are considered from both a physical obstruction and a timing point of view. Physical hierarchies are honored and RTL partitions are correctly assigned within the appropriate physical boundaries. Timing estimation is more accurate because real physical implementation and delays are factored in during synthesis, resulting in a reliable and predictable design flow. The new RTL synthesis and floorplanning tools can shrink overall design time from weeks to days.

New RTL floorplanning strategies

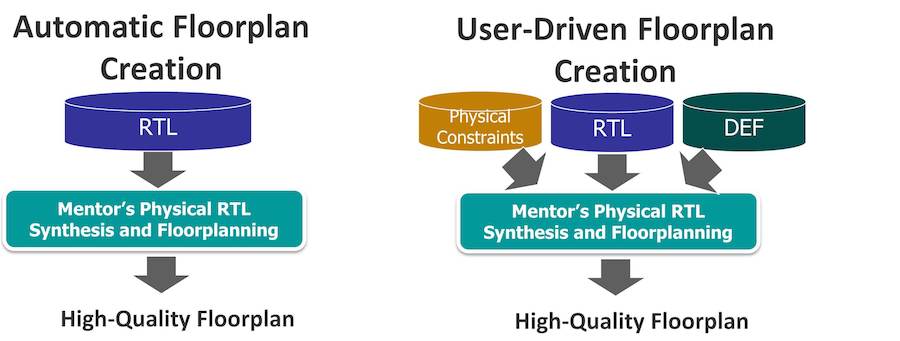

There are two news ways to generate floorplans with the emerging tools (Figure 2- click image to enlarge):

- Data flow-driven automatic floorplanning. This automatically generates a floorplan. The RTL input is partitioned into atomic partitions within the user hierarchies based on the functionality. Automatic floorplanning employs design utilization information and performs timing-aware macro and pin placement based on connectivity without the need for physical constraints from the user.

- User-driven floorplanning. This incremental exercise is based on the physical constraint inputs such as die size, or existing macro or pin locations. Once the die size is defined by the user or uploaded from a DEF, the pins and macros are placed in an incremental fashion. The GUI provides advanced floorplan editing capabilities.

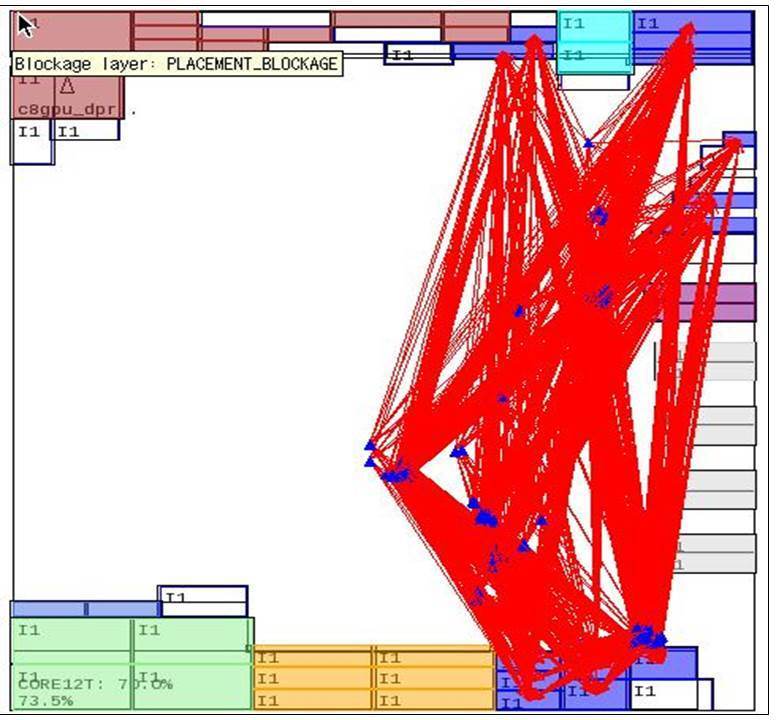

The new tools can automatically create a seed floorplan that can then be analyzed and edited. Designers can perform flyline and connectivity analysis between regions before placing the physical partition regions (Figure 3- click image to enlarge). The floorplanner automatically shapes and resizes the regions for the best fit based on the die size and utilization constraints. I/O pin placement is driven by the macro and RTL module connectivity and users can assign pins to specific edges.

Designers can then refine the seed macro placement. The macro step finds the optimal configuration for the macros based on timing, connectivity, wire length, and minimizing overlaps. Congestion-aware macro packing ensures that there is space between macros to eliminate congestion problems during implementation. Designers can also run multiple macro placement runs in parallel and compare different design metrics for each of the macro placement configurations before deciding on the best configuration for implementation.

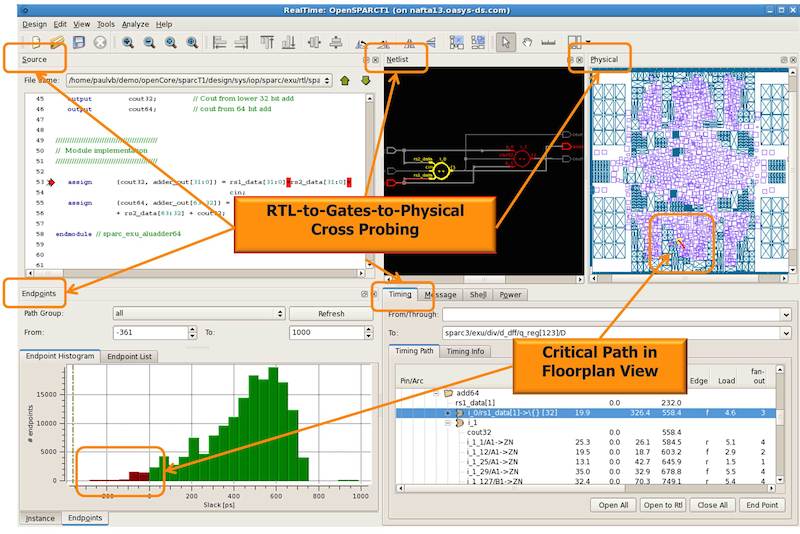

Integrated cockpit and cross probing is another feature found in the new tools. These allow designers to cross-probe between physical and RTL databases. The tools provide all the design views in a single platform – from logical to physical to timing. They also provide different physical views for early debugging including a static/dynamic power map, congestion map, critical timing map, and hierarchical floorplanning view (Figure 4- click image to enlarge).

Figure 4. Cross-probing lets designers to make changes and re-run synthesis quickly (Mentor Graphics)

New physical RTL synthesis and floorplanning tools also have very good correlation to back-end physical implementation tools, which reduces front-end to back-end iterations. The RTL synthesis and floorplanning engines use a unified global router-based topology prediction that enables back-end accurate congestion modeling.

The new tools also excel on speed and quality of results. Designers can expect RTL synthesis and floorplanning to handle full‐chip designs of up to 100 million gates and be up to 10x faster than the traditional physical synthesis tools with equal or better quality of results.

Summary

Next generation RTL synthesis and floorplanning tools are able to provide floorplanning capabilities during RTL synthesis. RTL-level floorplanning significantly reduces the front-end to back-end iterations and reduces total design turn-around time, with up to 10x faster synthesis run times compared to traditional synthesis tools and 100+ million gates design capacity to tackle the growing design sizes with ease with a compact memory footprint.

Further reading

*Learn more about this topic in a free whitepaper from Mentor Graphics, Next-generation RTL Floorplanning.

About the author

Sudhakar Jilla is the group marketing director at Mentor Graphics for all the company’s implementation and signoff closure products including those for RTL floorplanning, physical synthesis, place & route, and signoff ECO closure.