No double-quick growth for DDR3

Lane Mason

Marc Greenberg

DDR3 DRAMs still languish around the edges of the market despite their supposed attraction in terms of power and performance, the widespread availability of product, and the presence of a supposedly ‘evolved’ ecosystem and implementation infrastructure.

Just over 18 months ago, Intel launched a major Go To DDR3 market initiative at its Developer Forum in Beijing. It had the backing of leading DRAM manufacturers, and chipsets supporting DDR2 and DDR3 were rolled out during fall 2007.

However, as this article went to press, none of the leading PC makers yet offered a mass-market DDR3-enabled system on its website. Some can be found from less well-known players and as ‘white boxes’ from Asia. A few more are appearing in high-end gaming machines, those with price tags in the $5,000-$6,000 range. But it looks like most of us will have to wait at least one more product-line refresh cycle before we see DDR3 DRAMs in the memory subsystem.

There is plenty to be said about DDR3’s slow development, and more ‘excuses’ seem to come to light every month. Still, the main reasons why the technology is ‘two years late’ can be summarized as follows:

- PCs have been the main market and roadmap driver for DRAMs, but the sector has changed its marketing focus from clock speed and similar performance benchmarks to factors such as low power, size and weight.

- Partly because of DDR3’s cost-to-build uplift for its larger die size, it remains relatively expensive. By contrast, DDR2 is quite cheap—under $17 for 1GB DDR2 DIMMs right now, a figure likely to drop again before the year’s end.

- There are also ‘price outlook’ uncertainties. Vendors are reluctant to jump into a technology until they can see far enough ahead to load manufacturing lines confidently.

- The DDR3 spec was delayed and is still not ‘locked’. Uncertainties remain (e.g., should one take the recently unveiled 1.35V option?)

- There have been delays in rolling out the technology’s infrastructure and ecosystem and, although they have evolved, some players still question their adequacy.

- More examples of DDR3-based performance benefits across a variety of systems are needed.

- There are disconnects between DRAM standards and designs, the transition timetable, and total system optimization. DDR2 in PCs has been seen overwhelmingly in the ‘667’ flavor. DDR1 held on in the market for far longer than expected.

- PC prices are declining steadily in real terms. This makes it harder to raise any subsystem price, even temporarily, regardless of the performance boost it offers.

Let’s flesh out a few of these issues to deepen our understanding of DDR3 DRAMs’ future development and deployment.

Pricing and price outlook

DDR3 prices are higher than DDR2 even for the same density and performance, though DDR2 prices are underwater when it comes to profitability. What vendor would drop DDR3 prices prematurely, selling the technology at a loss to build a market? Those who forecast DDR3 at within 10% of DDR2 by the end of this year would have been disappointed again by the resumption of DDR2 price competition in late summer. DDR2 is therefore way ahead as the high-volume runner and will get first refusal on new technologies, die shrinks and other resources for a while longer. By volume, 1GB DDR2-667 probably outsells 1GB DDR3 by 25X today.

DDR3 is further handicapped by its larger die size, a result of technical improvements needed to deliver its higher performance (i.e., finer segmentation of the array, on-chip driver calibration, universal on-die termination (ODT)). DDR3 parts analyzed by Semiconductor Insights (www.denali.com/eda

techforum/ddr3_die_designs) point to a 15-20% die penalty for DDR3, translating into a 15% build cost penalty (however, Micron says that its DDR3 die is now only 3% larger than DDR2 with the same functionality, and Hynix says its 1GB DDR3 is just 7% larger than its DDR2).

Intel

Intel made a song and dance about DDR3 in Beijing

Price visibility, line loading, profits and ‘permanence’

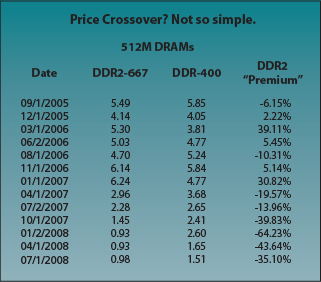

The first price crossover to a new technology often may not stick. Consider the clumsy, ill-advised transition from DDR1 to DDR2. Manufacturing lines were loaded with DDR2 prematurely, causing a glut and low prices. Then, many DRAM makers backed away from DDR2, and flushed out lines with DDR1 as those parts showed greater tenacity than expected.

Historical pricing data from DRAM Exchange shows how the initial glut caused DDR2 to become cheaper than DDR1 in Q405, but once DDR1 reasserted itself, DDR2 again became a premium-priced part, costing about 40% more by March 2006 for a 512MB part. DDR2 did not actually reach stable price and production cost points below those for DDR1 until Q207, by then the third crossover (Figure 1).

DRAM makers want to avoid seesaw pricing for DDR3—and, so far, their reticence looks pretty smart. It seems that the roll out of DDR3-enabled PCs is following a more rational path, starting with the highest-cost and highest-performance segments, and moving gradually down the PC product line.

The PC landscape has changed

A few years ago, the PC industry and Intel stopped chanting ‘clock speed’. They started looking more at system performance, and within those criteria, at power as an increasingly important system product differentiator. As noted earlier, PCs are today also sold on metrics such as form factor, battery life, compatibility with smaller portable devices and more robust operating systems. That these are all now strong and steady trends can be seen from the fact that laptop PC sales will surpass desktop sales for the first time in 2009.

Declining price points across different PC segments, regardless of system performance, are also a fact of life. So, until a stable and permanent DDR2-to-DDR3 price crossover takes place, adoption of DDR3 will remain sluggish. Moreover, a whole new class of low-end products has emerged (e.g., netbooks, ‘ultra low-cost’ and ‘ultra mobile’ PCs and Mobile Internet Devices). It is not seen as an early adopter of DDR3 DRAMs, but does highlight important changes taking place in the PC industry.

DRAM roadmap

If you compare the DRAM product definitions from various standards committees with how they contribute to and influence system costs, specifications and benchmarks, you might conclude that there is something of an intrinsic mismatch.

For example, DDR2 did not outgun DDR1 PC benchmarks in any substantial way until DDR2-667 went into high-volume production during early 2006. Although DDR2 has long had 533, 667 and 800 bins that exceed DDR1’s top bin of 400, the overwhelming bulk of DDR2 shipments into the PC space have been 667 (potentially as many as 90% of DDR2 DRAMs used in PCs). The industry is showing little enthusiasm for DDR2-800s or the late-arriving DDR2-1066.

Denali Software

FIGURE 1 The DDR1-DDR2 price crossover took time

As with the move from DDR1 to DDR2, the major MPU vendors, AMD and Intel, have different views as to what constitutes the right conditions for the most cost-effective transition to DDR3. Intel wants the faster transition, while AMD seems content to wait, perhaps until DDR2-1066 is in place in systems.

Again taking history as prologue, there was once the notion that successive PC product line refreshes would take larger quantities of faster DDR2 chip speeds. In fact, after a short-lived move to DDR2-533, once DDR2-667 came to dominate, things coalesced at that level. This seems to indicate that the system price performance benefit deriving from faster DRAMs is hard to forecast, harder still to implement and optimize (particularly given a confusing variety of ‘options’), and hard to execute. The latest move to adopt a 1.35V operating voltage for DDR3 further confuses that technology’s roadmap and, once more, makes system optimization more complicated.

DDR3 and embedded applications

Embedded applications have their own issues with memory technologies, but are not immune from the travails of DDR3 DRAMs in the PC market. PCs account for so large a portion of the DRAM supply line that they effectively set prices, manufacturing programs and the DRAM industry’s overall direction.

Many embedded applications want, and can use DDR3, but designers have hedged their bets. They are working on combo designs that straddle the DDR2-DDR3 threshold until they have a clearer picture of the DDR3 market’s longer-term outlook.

There are some power users in the embedded space who have decided that their need for DDR3 outweighs being price-sensitive. They have forged ahead and are using DDR3 today in modest volumes, paying more to access the better power performance inherent in the technology and the 1333 and 1600 data transfer rates it offers. This is, however, a relatively small group.

Technical dreams and nightmares

Some describe DDR3 as a DRAM dream or nightmare, sometimes both. By introducing the features needed to support ‘fly-by’ routing, DDR3 solves most problems faced by memory devices placed in a DIMM environment. Demands on the DIMM address and control busses are significantly reduced, and the address and control busses enjoy a single end-of-line termination. The DIMMs are arranged so that both writes and reads are slightly staggered across the chips on the DIMM, reducing the risk of simultaneous switching outputs (SSO) for both the DIMM and the chip driving it. The ODT method has been improved for better signal integrity on the memory bus, particularly when the system uses several DIMMs. The concept of driver calibration, introduced for DDR2 but quietly ignored by most manufacturers, is in the DDR3 specification in an improved form.

For DIMM and non-DIMM applications, the speed of DDR3 reaches 1.6Gb/s per pin under the current specification, with rumors of 1.866Gb/s and 2.133Gb/s on the horizon (indeed, Elpida says it has a 2.5GHz 1Gb DDR3 DRAM, operating at both 1.35V and 1.2V). The lower voltage requirement of DDR3 helps to save power in servers and set-top boxes alike (although note that power is proportional to frequency, which means that frequency increases can effectively cancel out some benefits from the reduced voltage). Still, at a given frequency, we would expect power consumption for DDR3 to be less than that for DDR2.

AV777

DDR3 is yet to move beyond gaming PCs

Most of the improvements to the DDR3 chips and DIMMs do significantly complicate the job of the memory controller on the chip that is driving the DIMM (this chip could be a North Bridge or a direct attach to the CPU or ASIC). For each chip on the DIMM, there is a slightly different timing domain for reads, and a slightly different optimal time for launching writes. A leveling sequence needs to take place to optimize the two.

In the PC domain, the economics of the system come into play. In the system, there is only one memory controller but there are probably two DIMMs (and 16 memory chips in most cases). So, it makes sense to have the complex work done by the memory controller. There are only a few memory controller designs that make it into PCs, so once again from a system perspective, the obvious advantages of DDR3 memory outweigh the increased complexity of interfacing to DDR3 devices.

For systems that bridge the transition to DDR3 (even those using a dual-mode DDR2/DDR3 memory interface), it should be remembered that DDR2 and DDR3 are incompatible at the voltage level, and only partially compatible at the protocol level. Therefore, DDR2 DIMMs are keyed differently to DDR3 DIMMs and one will not fit the socket for the other. The result is that you must either redesign the PC board on moving from DDR2 or DDR3, or use a system board with separate DIMM sockets for the two technologies.

Embedded dreams and nightmares

Embedded systems that use DIMMs can have issues with the larger pre-fetch size of DDR3. Most level 2 cache lines in embedded systems are 32byte. Since a DIMM is 8byte-wide and a DDR3 pre-fetch is eight transfers, 64byte are transferred with each transaction to a DDR3 memory, and half of this must be thrown away if the destination of the transfer is a 32byte-cache line. DDR3 does have some backwards compatibility modes to make it compatible with the 4n transfer mode of DDR2 and earlier memories, but they are much less efficient than the original.

Zyrex

Low-cost netbooks do not need high-end chips

Embedded systems not using DIMMs may not need all the complexity associated with driver calibration, write leveling, and so on. For those systems using just one memory chip, there is no real difference between DDR3’s fly-by routing and DDR2’s balanced-tree routing. For those systems using two memory chips, balanced-tree routing would be used with both DDR2 and DDR3 in most cases, ignoring DDR3’s fly-by capabilities. These systems may not use the drive strength calibration modes of DDR3, particularly at lower speeds of operation.

Many embedded systems need only a small amount of memory. DDR2 parts as small as 256MB are still available from several sources, but for DDR3, we expect the few ‘entry level’ 512MB parts to give way to 1GB parts very soon. It follows then that if PC systems are waiting for cost parity on a per-bit basis before they move to DDR3, it will be an even longer wait before embedded systems with limited memory requirements move to 1Gb DDR3 parts.

Finally, for all embedded systems, the minimum clock frequency of DDR3 memory is 300MHz, which can be too fast for some modes of operation (there is a DLL-off mode for operation below 300MHz, but it can be problematic). While the maximum clock speed of DDR3 is double that of DDR2, the read latency of the memory—a key determinant of embedded system performance—is relatively unchanged between the two technologies, with parts available in the 13-15ns range.

Conclusion

DDR3 offers a lot of technical advantages for PC and server applications using DIMMs. DDR3 can also offer more bandwidth, more density and reduced power consumption for newer PC and server-type systems. We therefore expect continued adoption of DDR3 in high-end systems, with the technology moving more into the mainstream as its market price approaches parity with that of DDR2.

For some embedded and non-PC systems, DDR3 may be too much of a good thing. While engineers here should design in combo DDR2/DDR3 support to future-proof products, the adoption of DDR3 in these products may only happen when it becomes significantly less expensive than DDR2.

Lane Mason is memory market analyst and Marc Greenberg is director, technical marketing at Denali Software. Further details on the company’s tracking of the DDR marketplace can also be found online at www.denali.com/dmr.