Exploring the advantages of monolithic Bluetooth low energy radio integration

The low-energy variant of the Bluetooth short-range wireless protocol (Bluetooth low energy) is being rapidly adopted in IoT applications such as wearables, tracking devices, and smart objects for home or commercial environments.

Many of these devices have been brought to market quickly by integrating standard parts, such as microcontrollers, memory and wireless interfaces, on a PCB. Although this brings first-mover advantage, it may mean that designers are yet to take full advantage of all the system partitioning options and integration opportunities that advanced process nodes can bring.

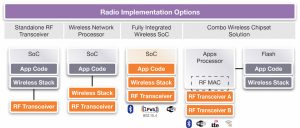

A variety of approaches to building wireless interfaces have emerged over the past few years (See Figure 1).

- Standalone RF transceiver chips include a controller and PHY, or in the case of Bluetooth, a Link Layer and PHY, and connect to the main SoC, which houses the software stack and application code.

- Wireless network processors have a dedicated processor to run the wireless protocol stack, offloading this work from the main SoC.

- A monolithic wireless SoC integrates the Link Layer and PHY into the SoC that runs all the software stacks and application code.

- Combo wireless chipsets combine several wireless technologies in a transceiver that is connected to the SoC, which includes the digital modem. All software, wireless stacks, and application codes are held in external non-volatile memory.

Figure 1 Bluetooth chip implementation options (Source: ti.com)

How do you choose which approach works best for your application? Process technologies play a part here:

- A standalone RF transceiver is likely to be built in a legacy node such as 180nm.

- A wireless network processor may be built on a mature 90nm node.

- Monolithic wireless solutions have gained traction in process nodes such as 90nm but current solutions are most likely to be built on a 40nm or 55nm node, because they can integrate embedded flash, plus a wide variety of mixed-signal and wireless IP.

- Combo wireless chipsets tend to use more advanced process nodes, at 28nm and below, to minimize die size and cost. These chipsets can use off-chip memory to give programmers more flexibility, but are also implemented as a set of three differing SoC devices.

This lists show that there are a variety of options for implementing wireless interfaces, which depend on the system architecture, partitioning, functionality and process technologies. In many cases, though, full monolithic integration is both possible and advantageous.

Let’s look at some examples. Current wearable designs, such as fitness bands, may consist of an SoC connected to a Bluetooth low energy IC via a UART or I2C bus. Similarly, virtual-reality (VR) goggles may use a standard Bluetooth wireless network processor to communicate with gaming controllers. Bluetooth low energy chipsets are also found in smart-home products such as door locks, lighting, and indoor location beacons. All of these could benefit from integrating the wireless functions into SoCs already in the system, to save cost.

Designs that also include a higher-bandwidth wireless technology, such as WiFi, will often use a wireless combo chip with multiple wireless technologies, a processor and external memories. Augmented-reality goggles usually need more processing power then their VR brethren, so designers use a similar system architecture as in mobiles.

To integrate, or not?

Process technology makes deep wireless integration possible, but should you do it?

Wireless network processors, such as standalone Bluetooth low energy chips, have usually been through rigorous certification processes, which makes it easier to certify any product that uses them. Designing with these chips is also well understood, which simplifies complex issues such as driving antennas.

On the other hand, a monolithic solution should mean lower power, costs and latency, as well as a smaller footprint on the PCB. The latency issue may be more important than it first seems, because reduced latency may let the processor remain idle for longer, saving power.

An integrated approach also cuts the number of packages, PCB pads and traces, and manufacturing steps involved in implementing a solution. An integrated approach may also simplify systemic power management, for example by doing away with the need for a separate power-management IC for the wireless interface. Each saving alone may be small, but together they can add up to a worthwhile contribution.

Designers may also want to choose integrated Bluetooth low energy wireless interface over WiFi, to save power. WiFi is specified to support data rates of up to 300Mbit/s, but uses between 40 and 100μW of transmit and receive transmit power, and a sizable amount of memory, to do so. On the other hand, Bluetooth low energy will support data rates of just 2Mbit/s (under the Bluetooth 5 standard) but uses less than 10μW of transmit and receive power to do so. If the lesser bandwidth of Bluetooth low energy is enough for your application’s needs, you can think about implementing your design with much less memory, and in a 40nm or 55nm process that can run on supply voltages down to 0.9V.

For the right application, such as IoT SoCs, the advantages of integrating Bluetooth low energy are clear. Bluetooth low energy brings extremely low-power wireless connectivity, and implementing it on 40nm or 55nm processes also enables the integration of power-management techniques such as DC-DC down-converters and the use of thick oxide technologies to cut active and leakage power. In the world of IoT, where battery life is king, this can be the clinching argument in favor of Bluetooth low energy integration.

Further information

Synopsys offers a wide range of wireless and analog IP options for 5G, WiFi and LTE for cellular, wireless 802.15.4 and Bluetooth technologies with optimized analog front-ends, data converters and a complete Bluetooth low energy IP solution with PHYs and Link Layer IP.

DesignWare Bluetooth Low Energy IP solution

Author

Ron Lowman is the strategic marketing manager for IoT at Synopsys responsible for driving the IoT strategic initiatives, working closely with many of the IP product marketing managers. Prior to joining Synopsys, Lowman spent 16 years at Freescale within their MCU division. His background includes stints in strategy, business development, product marketing and engineering roles supporting IC test for automotive engine controllers, and factory automation and controls design. Lawman holds a Bachelor of Science degree in electrical engineering from The Colorado School of Mines and a Master’s degree in business administration from the University of Texas in Austin.

Ron Lowman, strategic marketing manager for IoT, Synopsys

Ron Lowman, strategic marketing manager for IoT, Synopsys