Supporting higher-resolution displays without major system redesign

Years ago, an HD screen cost thousands of dollars, burned hundreds of watts, measured tens of inches across, and was mounted in pride of place in the TV rooms of those lucky enough to afford it. Today, high-end smartphones, automotive infotainment systems, augmented reality (AR), and virtual reality (VR) devices are being introduced with quad HD or 4K resolutions, faster frame rates and support for RGB formats.

This radical change in the way that we use high-resolution displays means new challenges for designers, especially those working on battery-powered devices. The challenges are inter-related and include managing the required data bandwidth to the screen while reducing power consumption and retaining visual quality. To make this possible, designers need access to a protocol that enables visually lossless data compression over established display interfaces such as the MIPI Display Serial interface (DSI).

The Video Electronics Standards Association (VESA) Display Stream Compression (DSC) standard offers this kind of visually lossless performance and low latency for ultra-high-definition displays. VESA has worked with the MIPI Alliance to add the DSC specification to the MIPI DSI standard. But how does the VESA DSC standard work, how does it enable compression rates of up to 4x while retaining its visually lossless quality level, and how can designers implement it quickly?

The bandwidth challenge

MIPI DSI provides low-power, low-latency and low-cost chip-to-chip connectivity, linking multimedia processors to displays or other multimedia systems-on-chip (SoCs). It is used in applications such as smartphones, tablets, advanced driver assistance systems, and multimedia. However, as the popularity of high-resolution displays grows, the specification’s bandwidth is proving a limitation.

MIPI DSI operates on the MIPI D-PHY physical link at 2.5Gbit/s per four lanes, yielding a maximum data rate of 10Gbit/s per link. However, high-end video requires greater bandwidth: a 4K display using 24bit RGB at 60 frames per second (FPS) requires 13Gbit/s (12Gbit/s for its active area); while a 3D 1080p display using 24bit RGB at 60FPS requires 12Gbit/s (11Gbit/s for its active area).

Bandwidth requirements for deeper color modes, as used on the high dynamic range panels currently being introduced, are even greater, with designers having to consider redesigning devices and circuits to drive more DSI data lanes or even adding more physical links, at considerable design time, cost and risk. Adding the VESA DSC standard to the MIPI DSI specification should make it possible to overcome such bandwidth limitations without wholesale changes to related ASIC or SoC architectures and system circuits.

The DSC spec

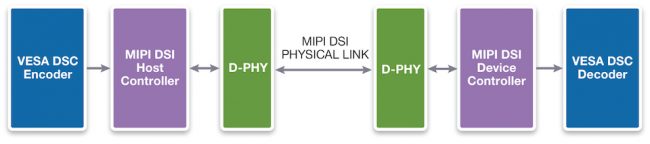

Incorporating DSC into the DSI standard has given designers of source and display devices a visually lossless way to transfer more pixel data over display links. Figure 1 shows a block diagram of VESA DSC integrated into MIPI DSI.

Figure 1 An example of how DSC and DSI interoperate on host and device sides (Source: Synopsys)

The VESA DSC algorithm can compress data at a constant bit rate, which creates a fixed-size data stream that can be transported by DSI without further processing or padding.

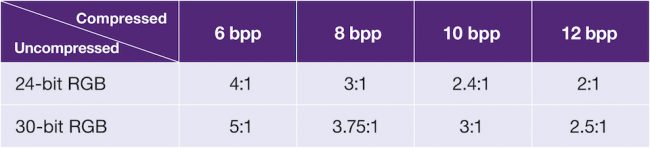

Table 1 shows the effect of applying multiple compression rates with DSC. For example, a 24bit RGB image normally transmits 24bit/pixel, but with DSC, this can be compressed to 12bit/pixel, halving the transmitted data rate. For the same 24bit RGB image, with DSC compressing it to 8bit/pixel, a 3:1 compression ratio is obtained. Image quality should be unaffected because DSC encoding is visually lossless.

Table 1 Sample compression rates with and without DSC (Source: Synopsys)

With VESA DSC, 4K and 3D 1080p video and image resolutions become possible over existing display links:

- 4K, compressed to 12bit/pixel @ 60FPS, requires 6.5Gbit/s – possible with three or four lanes

- 4K, compressed to 8 bit/pixel @ 60FPS, requires 4.4Gbit/s – possible with two, three or four lanes

- 3D 1080p, compressed to 12bit/pixel @ 60FPS, requires 6Gbit/s – possible with three or four lanes

- 3D 1080p, compressed to 8bit/pixel @ 60FPS, requires 4Gbit/s – possible with two, three or four lanes

How DSC works

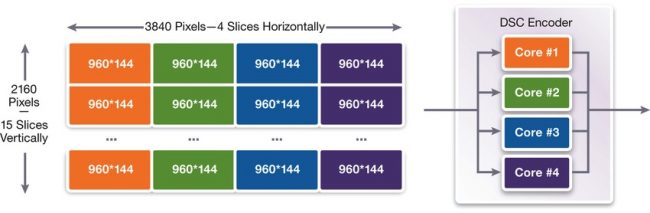

Each image is divided into a grid of slices before it is compressed. Slices are coded and decoded independently, to ensure transmission errors aren’t propagated among them. A DSC encoder can be made up of multiple cores operating in parallel. Figure 2 shows a 4K image (at left) being split into four columns by 15 rows, so that each resulting slice can be compressed in parallel by the corresponding DSC cores (indicated by color).

Figure 2 An example of a 4K (3840x2160) resolution image divided into slices, to be compressed in parallel (Source: Synopsys)

Since DSC does not compress data by analyzing adjacent frames, there is little latency and implementing the standard requires less embedded memory than compression standards such as H.264 or H.265. DSC’s compression algorithm is also designed to be directly implemented in hardware without the need for multimedia processors, to achieve greater area and power efficiency. With the appropriate architecture, DSC decoders can process three pixels per clock cycle, enabling systems designers to use lower clock frequencies. This is ideal for supporting newer technologies such chip-to-glass liquid-crystal displays.

Conclusion

A visually lossless compression standard such as DSC can help designers support quad HD or 4K resolution displays over the limited bandwidth of today’s display links, helping to avoid costly and risky circuit redesigns.

Synopsys has integrated VESA DSC into its silicon-proven DesignWare MIPI DSI IP which, together with the DesignWare MIPI D-PHY IP, provides designers with a complete display solution.

Further information

DesignWare MIPI DSI Host Controller IP with VESA DSC Encoder Datasheet

Author

Pedro Ricardo Miguel is a senior ASIC digital design engineer at Synopsys with more than 13 years of digital design experience focusing on digital signal processing, analog-to-digital and digital-to-analog converters, MIPI interfaces and image data compression. Miguel has a Master’s degree from University of Coimbra in Electronics and Computer Engineering.