Applying sub-threshold circuit techniques to IoT device design

Operating at near-threshold or sub-threshold voltages reduces static and dynamic power consumption, at the cost of design complexity.

The quest for denser IC processes operating at lower power has seen a steady reduction in supply voltages, which cuts both static and dynamic energy consumption. Operating at near-threshold or sub-threshold voltages reduces this further, at the cost of having to overcome a number of circuit design and characterisation challenges.

Sub-threshold advantages

To recap, a transistor’s threshold voltage (Vth) is the voltage at which the transistor turns on. Most transistor circuits use a supply voltage substantially greater than the threshold voltage, so that the point at which the transistors turn on is not affected by supply variations or noise.

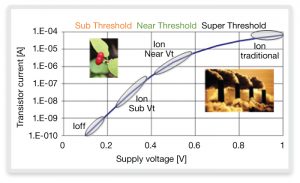

In sub-threshold operation, as shown in Figure 1, the supply voltage is well below the Vth of the transistors. In this region, the transistors are partially On, but are never fully turned On. In today’s process technologies, this region is at about 200 – 400mV.

Near-threshold operation happens between the sub-threshold region and the transistor threshold voltage Vth, or around 400 – 700mV for today’s processes.

Figure 1 Typical CMOS transistor operating regions (Source: Synopsys)

Static power consumption scales down linearly with the reducing supply voltage, but dynamic power consumption scales down much quickly in proportion to the square of the supply voltage.

The challenges of using sub-threshold technology

Sub-threshold transistor operation is not new, but working with the techniques has challenges that have prevented it from being widely applied.

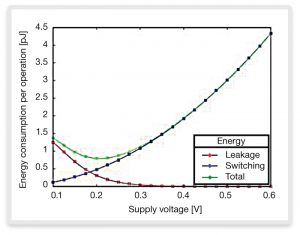

One such challenge is working out how much the supply voltage can be reduced before the leakage current dominates the dynamic (switching) current. Figure 2 shows that dynamic power continues to drop as the supply voltage is lowered, but process-driven leakage currents start to rise. The trick to using sub-threshold techniques effectively is to find the supply voltage at which the combination of leakage and dynamic power reaches its minimum.

Figure 2 Energy consumption as a function of supply voltage (Source: Synopsys)

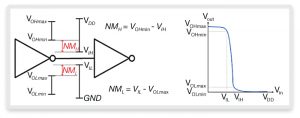

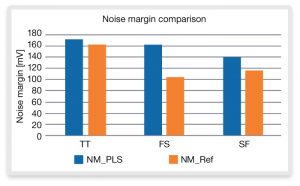

Sub-threshold circuits are much more sensitive to noise than those operating at higher supply voltages, with noise margins that are several orders of magnitude less. Typical super-threshold designs will see noise margins of hundreds of mV, which can drop to less than 100mV in a sub-threshold design. Standard-cell developers must try to design cells that claw back some of this loss of noise margin (NMH and NML in Figure 3).

Figure 3 Noise margin calculations for standard cells (Source: Synopsys)

Process and temperature variations are also more critical in sub-threshold designs as these can cause significant yield and performance problems.

Since most foundries’ standard-cell libraries are optimized to operate with supplies of ~0.9V (+/- 20%), their transistor models tend not to be accurate at sub-threshold voltages. Many IC vendors who want to use sub-threshold techniques are building their own standard-cell, memory and analog circuit libraries, which they can be sure are properly characterised at these challenging operating conditions.

Bringing sub-threshold designs to market

A few IC vendors are starting to use near/sub-threshold techniques, especially in battery-operated applications such as the IoT. Synopsys and PLSense (South Yokneam, Israel) have worked together to implement Synopsys’ ARC processors and subsystems using PLSense’s sub-threshold libraries and design techniques, to understand the potential systemic energy savings.

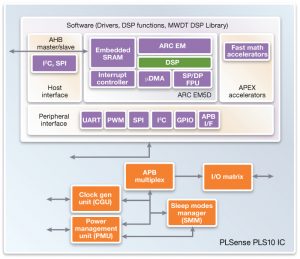

Figure 4 PLSense PLS10 IC based on Synopsys’ ARC Data Fusion Subsystem (Source: Synopsys)

The PLS10 IC operates between 0.45V and 1.1V from a battery. An adaptive dynamic voltage control algorithm adjusts the operating voltage to achieve the required clock frequency.

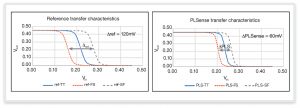

PLSense’s designed its sub-threshold cell library to minimise the voltage variance between the “fast NMOS/slow PMOS” (FS) and “slow NMOS/fast PMOS” (SF) process corners (Figure 5). It was also able to improve the noise margins for these corners (Figure 6), compared to standard foundry libraries.

Figure 5 Sub-threshold transfer characteristic comparison (Source: Synopsys)

Figure 6 Noise margin comparison for various process corners (Source: Synopsys)

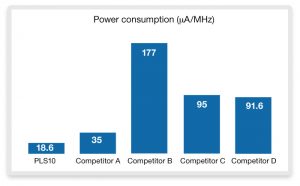

Using benchmarks such as EEMBC CoreMark, PLSense claims its approach offers up to nine times lower power consumption (measured in mA/MHz) than competitive low-power ICs, including other near/sub-threshold MCU designs (Figure 7).

Figure 7 Power consumption comparison vs competitive solutions (Source: Synopsys)

Conclusion

Operating with near-threshold or sub-threshold supply voltages can cut power consumption, at the cost of having to develop cell libraries and design methodologies that can overcome some of the technique’s limitations, such as susceptibility to noise and process variations. However, in markets such as IoT devices, where every Joule of energy saved means a few more minutes on the battery life, it may well be worthwhile.

Further information

Case Study: PLSense achieves 0.45V operation with sub-threshold technology implemented on Synopsys’ ARC Data Fusion IP subsystem

Author

Rich Collins is a product marketing manager at Synopsys.