Planting seeds

The 17th annual PCB West Conference and Exhibition takes place this year at the Santa Clara Marriott, September 14-19. For 2008, the conference’s theme is “Grow your knowledge in the heart of Silicon Valley.” This is an approach intended to reflect some of the obvious hot button issues in board design (e.g., high-speed, lead-free, etc.) as well as others the organizers may need more of a push for attention.

With the focus on education and training, the full event offers nine one- and two-day professional development courses, a new three-day course on High Speed and Simulation Tool Use by the technology’s very own ‘ratchet man’, Lee Ritchey, and a three-day technical conference made up of 28 workshops, panel sessions and half-day seminars. Most attendance, however, will gather around two exhibition days (Tuesday, Sept. 16 and Wednesday, Sept. 17), the first of which is Free Tuesday, when all of the technical sessions and exhibits are open to all attendees free of charge.

Free Tuesday

Unlike the conference’s backbone courses and technical sessions, Tuesday’s sessions are open to all attendees free of charge. The 2008 highlights include:

9 am – 11 am

PCB Design, Fab and Assembly Roundtable:Understanding the Dynamics of the Cost/Technology Equation Across the Supply Chain

Moderator: Terry Heilman, Sunstone Circuits

11 am – 12 noon

Keynote: Bringing Design to Life

Speaker: Dr. Chris Urmson, Carnegie Mellon University

1 pm – 2 pm

If You Can Make It, They Can Fake It: Counterfeit Parts and China

Speaker: David Ackerman, Ackerman-USA

1 pm – 2 pm

Becoming a Certified Military/Aerospace Supplier

Speaker: Steve DeWaters, Penumbra Strategies

2 pm – 3 pm

Death of a PCB Salesman

Speaker: Greg Papandrew, Bare Board Group

2 pm – 3 pm

ECAD/MCAD Collaboration

Speaker: Larry Kenyon, Mentor Graphics

3 pm – 4 pm

The Effect of COTS (Commercial Off-The-Shelf) on Defense Supply Chain Integration

Speaker: Steve DeWaters, Penumbra Strategies

4 pm – 5 pm

Lead-Free Cost Reductions

Speaker: Yash Sutariya, Saturn Electronics

“Designing for high-speed is the subject that really does stand out,” says Kathy Nargi-Toth, conference co-chair and editor of Printed Circuit Design and Fab. “It’s an obvious one, yes, but designers are still very hungry to hunt out nuances and ways of making improvements. We’ve got more people speaking on that than anything else.”

Across the whole program, 10 sessions, including several of the larger courses, specifically address high-speed, while many others touch on closely related areas.

“However, it’s also part of the conference’s job to highlight other things that are happening out there, issues that are just emerging,” says Nargi-Toth. “And there’s a couple of interesting areas there in DFM [design-formanufacture] and FPGAs.”

Alongside Free Tuesday’s keynote (see p.9), one of the opening day’s other highlights will be a roundtable looking at the relationship between design and the back-end. “What we’ve done is get a bunch of CTO-level fabricators and people in the assembly end to come along. And what we want to do is really address some of the issues around laminates and component selection and lines & spaces from a real DFM perspective,” says Nargi-Toth. “Again, there are things that get talked about here, but the designers don’t often get the chance to really pick these guys’ brains.” On the programmable logic front, Thursday (September 18) will see Bruce Riggins of sector EDA specialist Taray present Bringing Order to the FPGA I/O Planning Madness.

“We’ve started seeing how FPGA is trying to displace ASIC for more than just prototyping, and I think our audience is just now coming to terms with where that fits in with challenges in board design,” says Nargi-Toth.

Riggins’ preview of his presentation makes part of the background to the growing problem very clear. “As FPGA silicon and pin count densities have steadily grown, so have the problems of designing them into PCBs. Higher pin densities lead to increased routing congestion as more and more signals converge into a smaller and smaller space on the PCB,” he says.

Finally, also expect the PCB world to exhibit some of its traditional sparkiness over a few issues. Halogen-free is likely to be center stage at PCB West, but lead-free and both Europe and China’s flavors of RoHS to control other hazardous substances are still around. “In lead-free, you do have a lot of people who might have previously been able to work under exemptions but now find that they can’t, so that still goes on,” says Nargi-Toth. “But the whole halogen-free thing is what has a lot of people scratching their heads right now.” “At one point, there was a lot of pressure there to take bromines out of laminates, but now that seems to have faded away – yet you’ve still had about 15 years of research into these halogen-free materials. Where does all that go now?” Some answers might be forthcoming when this specific topic goes before one of the conference’s panel sessions on Wednesday (1:30pm-3:30pm).

There is plenty of scope for plenty of answers within the main program, all in line with the educational emphasis set by this year’s theme. However, one question that all those sessions will not answer concerns another hotly anticipated PCB event that runs in parallel with the main conference. And that question is, “Will anybody match Randy Holt?” With PCB West just around the corner, that also means it is time for the PCB Top Gun Hall of Fame competition to get under way again. Over two days, those engineers who are brave enough to put their skills (and their egos) on the line go through a series of tests, including a written exam, personal interviews, and an actual design. And for 2008, the bar has been raised. Last year’s winner, Holt, an engineer at Optimum Design Associates, did not just defeat his rivals, he became the first competitor to receive a flawless score for the design portion of the competition.

So, it should be a busy show, entertaining and educational for all attendees. Register online and review the full program now at www.pcbwest.com.

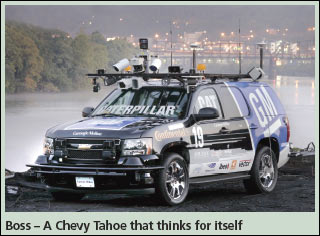

Who’s the boss?

DARPA’s search for an autonomous robotic vehicle and its frequent ‘challenges’ to researchers in the field took on a new twist last year. The old Grand Challenge became the 2007 Urban Challenge. Competitors had to negotiate not the desert, but a mock city course with some automated and also some real-life, manned obstacles in their way.

This was not about who finished first as much as it was about whose vehicle showed the best adherence to California’s driving rules. Proof – were it needed – of just how far robotics technology has come.

The winning team, Tartan Racing from Pittsburgh, PA., went away with a check from the research agency. At PCB West, attendees will have the chance to learn a little more about how Tartan’s vehicle, the self-confidently named ‘Boss’, earned its triumph. The conference’s 2008 keynote speaker is Dr. Chris Urmson, director of technology for the Urban Challenge Robotics Institute at Pittsburgh’s Carnegie Mellon University and, more to the point, Boss’ inventor.

At PCB West, he will discuss the role of semiconductors in the automotive world, but he will also get down and dirty over what more people want to hear about – specifically, the architecture underpinning this extraordinary vehicle with its 300,000 lines of code, and more than a dozen lasers, cameras and radar systems with which it views and navigates the world.