Making the move to ESL hardware design

Electronic system level (ESL) is typically defined as design above the register transfer level (RTL). When applied to hardware design, ESL is the process of describing hardware functionality at higher levels of abstraction to increase designer productivity and enable greater degrees of exploration. With ESL, hardware designers no longer spend most of their time designing and verifying RTL code.

This seems straightforward, but ESL hardware design presents engineers with a set of noteworthy challenges. These include learning new languages, understanding how to produce quality RTL implementations from system-level code and successfully introducing new EDA tools into the design flow.

That said, ESL has now been around for more than 10 years, more and more semiconductor companies are using ESL tools, and consequently ESL methodologies are rapidly maturing.

This paper illustrates that increasing maturity by describing a system level-to-RTL design flow. It looks at the issues involved in switching to ESL hardware design and provides insights into some of the appropriate design and verification tools.

Electronic system level (ESL) techniques have been around for more than a decade. Early ESL design involved system architects writing sequential C code to model new algorithms. There were few, if any commercial tools, and hardware implementations were disjointed, linked only by specification documents derived from ESL results. ESL has since evolved into a set of complementary methodologies that enable hardware/software co-design, system-level verification and hardware design. ESL tools automate the path from system-level models to RTL implementation.

Analyst Gary Smith began to track ESL tools as part of the EDA landscape in 1994 (1). Initially, the tools concentrated on system modeling and hardware/software co-verification. There were few vendors and also few standards. At 2005’s Design Automation Conference, by contrast, there was a sizeable list of companies marketing a much broader range of ESL tools.

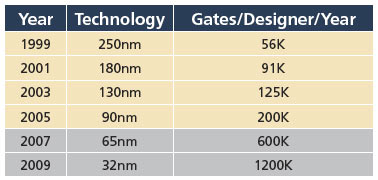

Figure 1. Technology impact on designer productivity. Source: ITRS 2007 Design Report

Motivation

Increasing design complexity is the primary motivation behind moves to ESL. An ‘average’ system-on-chip (SoC) design has more than 20 million gates; the gate count for a large design can exceed 100 million. There are also the demands of a mushrooming number of hardware features, a plethora of standards to address and incorporate, and the presence of thousands and thousands of lines of embedded software code. It is clear that productivity enhancements are required. A forecast from the International Technology Roadmap for Semiconductors (ITRS) sets out the increasing burden on the designer in stark terms (Figure 1).

ITRS’ 2007 System Drivers report states, “Maintaining constant SoC design effort requires a 10X design productivity improvement for newly designed logic over the next 10 years to 2018. To solve this productivity challenge, several approaches must be combined. First, design abstraction levels must be raised. Second, the degree of automation, particularly in design verification and design implementation, must be increased. Finally, reuse rate must be increased, with an accompanying reduction in effort overhead for design reuse also being required.”

Early adopters of ESL have tended to be those leading-edge semiconductor companies already known for pushing semiconductor and associated design methodologies to the leading edge. (2) Of these, many are already realizing a return on their ESL investments. For example, K. Wakabayashi of NEC noted in a presentation during the 2008 Design Automation and Test in Europe conference, that his company has fabricated more than $2bn worth of chips using C-based design.

Defining an ESL hardware design flow

Good RTL design is based on writing code that produces a ‘quality’ implementation—and ‘quality’ here means an implementation that produces functionally correct results within prescribed system constraints such as timing, power and area requirements. The bulk of the RTL designer’s time and talent goes into coding and verification to achieve these quality goals.

In most cases, it is impractical to recode micro-architectures or algorithms once RTL meets a sufficient quality level, even if a better implementation might be possible. RTL verification amplifies this obstacle by adding time for test development and simulation runtimes.

ESL changes the dynamic by moving hardware design to higher levels of abstraction, freeing the designer from a preoccupation with the detail of state machines and bit-level implementations. It improves productivity and allows the assessment of multiple implementations.

Since system models run 1,000 to 10,000 times faster than RTL designs, system-level verification takes less time and has better functional coverage. This translates into a shorter development cycle. Looking from another angle, ESL allows hardware designers to produce more functionally correct logic in a given amount of time.

To take advantage of ESL methods, hardware designers must first understand the difference in abstraction between system-level and RTL languages. ESL is a matter of using a new language—usually C, C++ and/or SystemC. Experience has shown that it is more difficult for software engineers to learn to design hardware than it is for hardware designers to learn to code using new software languages.

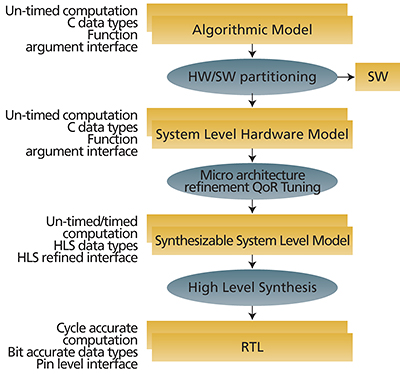

Figure 2. Levels of ESL models. Source: Calypto Design Systems

An ESL design flow consists of different types of ESL models (Figure 2). There are several distinct levels with multiple refinements of those models carried out at each.

The highest-level model is purely functional with no consideration for the final implementation. It is fast, retargetable and broadly reusable. Together with models of the system environment, designers can accurately reproduce or even fit it into the end-user application for verification. Since the purpose of such models is to prototype and prove the functional correctness of algorithms, speed and flexibility are at a premium as designers iterate to find the best algorithms and differentiate the end product.

Next is system-level architectural design. This separates the hardware function from the software function. The system-level hardware model is further partitioned and hardware interfaces are added so processor models and hardware adaptation layers can be defined. Most hardware functionality exists as algorithmic computation. The original test environment remains and these models still run fast enough to be verified with real-world applications and run application software. The architectural level is where hardware designers carry out performance tuning and architectural trade-offs.

From here, software and hardware are developed independently. The architectural model establishes an agreed-upon hardware/software interface and compatibility is maintained throughout software and hardware design.

At this stage in the flow, hardware designers turn algorithms into hierarchical system-level descriptions that include control logic, block-level interfaces, statically-sized resources and defined memory types. This requires a knowledge of hardware design and an understanding of how system-level languages get mapped onto hardware implementations. Since hardware designers working at the system level do not have to worry about micro-architecture details and cycle-accurate timing, it is possible to quickly iterate through many alternative system-level designs to find the highest quality implementation. This is not possible with RTL design.

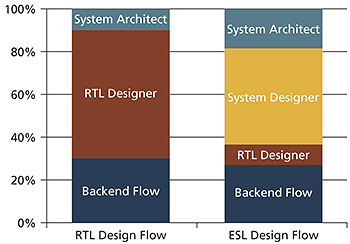

Figure 3. RTL design moving to the system level. Source: Calypto Design Systems

Once the synthesizable system-level model is complete, ESL tools automate the process of creating and verifying RTL code. These tools and their operation are covered in the next section. Just as the adoption of RTL design significantly reduced the amount of gate-level design and verification, ESL reduces the time spent designing and verifying RTL code. The job of the hardware designer has moved from RTL coding to system-level hardware design (Figure 3).

ESL design and verification tools

ESL design and verification tools automate the translation of system-level models into RTL implementations, making the process predictable, reliable and efficient. The promise of high level synthesis (HLS) has become a reality as system-level design implementation tools are rapidly maturing and an ecosystem has grown around them. Companies have cited the ability of these tools in certified flows. (3)(4)

HLS improves productivity in two ways. First, it saves design time by reducing the number of lines of code needed to describe hardware functionality. Second, HLS tools can generate multiple RTL implementations from a single system-level model by changing only a few constraints such as latency, throughput and resource sharing. With HLS tools, designers can quickly create a handful of potential implementations to evaluate against power, area and timing requirements, making it easier to reach the highest quality RTL implementation.

Design teams using HLS typically report a 10X improvement in design productivity using system-level design over RTL. Forte Design Systems, for example, claims that its customers are designing about 1.5 to 2 million gates per year per designer using HLS compared to an average of 200,000 gates for RTL. Similarly, Mentor Graphics presented a customer example of a vehicle tracking design block that was implemented in two weeks using its Catapult C synthesis, where 32 weeks would have been needed for the same design in RTL.

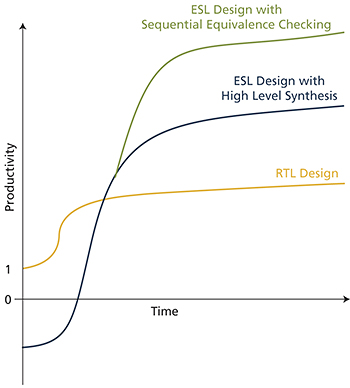

Sequential equivalence checking (SEC) increases the productivity gains from HLS (6), verifying the output of HLS without requiring the investment in testbench development and time-consuming RTL simulations. More important, with SEC, designers can be confident that all corner cases are covered without analyzing unfamiliar, machine-generated RTL code.

SEC is a functional technique that formally verifies equivalence between two designs. Unlike combinational equivalence checkers that require a one-to-one mapping of state elements, SEC supports differences in the level of design abstraction and state.

Figure 4. Relative design productivity. Source: Calypto Design Systems

SEC gives independent verification of HLS results by comprehensively verifying that two designs are functionally equivalent or producing a short, concise counter example in the form of a waveform trace. In ESL hardware design flows, HLS combined with SEC provides a path to functionally proven, high-quality RTL code.

Just as logic equivalence checking (LEC) is a part of every RTL synthesis flow, SEC is an integral check and balance in HLS flows. Similar to LEC automation during RTL synthesis, links between HLS and SEC automate the ESL verification flow.

STMicroelectronics (ST) has created an advanced ESL methodology based on high-level synthesis and sequential equivalence checking to improve design and verification productivity. The methodology allows ST to design at the system level and keep the various models in sync with its original ‘golden model’.

SLEC System-HLS from Calypto Design Systems is a sequential equivalence checker that is tightly linked with HLS tools and supports system-level languages including C/C++ and System C. SLEC finds bugs in ESL flows caused by ambiguities between system languages, user errors and HLS tool bugs. SEC can comprehensively verify blocks in minutes that would otherwise take weeks to verify using simulation regressions.

Conclusion

Key enablers for ESL hardware design include tightly integrated HLS. Just as mature RTL synthesis flows require automated formal methods, ESL flows require SEC to eliminate block-level simulations and ensure RTL code generated from HLS is functionally equivalent to the system-level model.

References:

(1) “Electronic Design Processes Workshop: Good engineers are worriers”, EDN, 4/19/2006. Available at http://www.edn.com/article/CA6326107.html.

(2) “Evolution of ESL Development”, ESL Design and Verification, Brian Bailey, Grant Martin & Andrew Piziali, Morgan Kaufmann, 2007

(3) “Mentor Graphics Catapult C Synthesis Adopted for Fujitsu Standard ASIC Design Kit, Establishes Electronic System Level Reference Flow for Customers”, Press Release, 1/21/2008

(4) “Toshiba Uses Forte Cynthesizer to Accelerate Completion of H.264 Multimedia Design”, Press Release, 1/26/2006

(5) ECSI New Wave of High Level Synthesis Workshop, Mar 14, 2008: presented by Pascal Urard.

Calypto Design Systems

2933 Bunker Hill Lane, Suite 202

Santa Clara

CA 95054

USA

T: +1 408 850 2300

W: www.calypto.com