July 28, 2020

It is easier than ever to build a flexible, resilient, and end-to-end hierarchical DFT flow with smart automation.

April 24, 2020

Learn how the latest design for test innovations deliver efficiency and profitability across the design flow.

November 7, 2019

It's the fiftieth International Test Conference this year. How much has been achieved and how much more work is there to do to ensure that we can keep building chips that do what they are supposed to?

September 13, 2019

SEMICON West showed a distinct thematic shift away from preserving Moore's Law to assessing the architectural implications of AI, as EDA was brought into the event.

August 15, 2019

Hierarchical DFT for Arm-based SoCs is easier than ever with the arrival of a complete reference flow from Mentor and Arm.

May 14, 2019

Part two of this feature describes three use-cases that exploit the VirtuaLAB technology in HDMI, PCIe and Ethernet designs.

May 1, 2019

This two-part article describes advantages when using a hardware emulation platform in virtual mode compared with in-circuit-emulation.

April 26, 2019

Portable Stimulus allows reuse along horizontal, vertical and technique axes, but you need to be aware of the strengths and weaknesses of each to get the greatest benefits.

February 27, 2019

This defect and fault injection primer looks at how to standardize definitions, decide injection volume, measure activity, manage simulation, optimize test time and more.

July 9, 2018

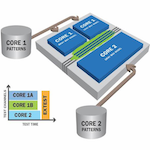

A hierarchical methodology removes DFT from the critical path for large designs. The methodology is compatible with other techniques such as channel sharing, which can further reduce ATPG turn-around time and test cost.