March 25, 2019

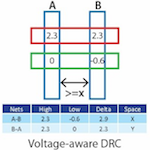

Automated voltage-aware DRC addresses the reliability verification challenges in today’s high-voltage and multiple power domain applications.

February 8, 2019

How to achieve efficient merging of data from formats such as OASIS, GDS, and OpenAccess to ensure timely verification through DRC runs.

January 25, 2019

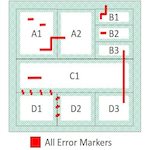

In a continuous-build design flow, at which level should your error markers be addressed?

October 16, 2018

How you can use the dedicated rule decks now being provided by foundries as the foundation for a reliability verification flow.

August 13, 2018

Dina Medhat describes what you need to know about the types of waiver strategy that can be applied.

April 23, 2018

Why design data integrity matters from cell design to tapeout. These techniques will help ensure your validation process is as comprehensive as possible.

January 15, 2018

How to get the best PV results by reducing computational demands; handling data more efficiently and exploiting parallelization.

December 22, 2017

In-design DRC is a technique that frees up engineers from many of the challenges of delivering AMS design under ever more complex design rules.

April 10, 2017

Hierarchical DFT is vital for large, complex designs. Users still to transition to the technique can nevertheless exploit its pattern reuse strategies as they move toward adoption.

July 20, 2015

In sessions at the 2015 Design Automation Conference, engineers who had worked on finFET-oriented projects revealed how the technology has changed their design practices and where others may want to think twice about making the move.