March 29, 2024

RISC-V adoption is growing fast as is the ecosystem around the open-source core. Hardware and software are now vital for appropriate debug.

January 12, 2022

Automated formal technologies can be used to ease the debug and functional verification burden of SystemC/C++ code prior to high-level synthesis. This tutorial, first presented at DVCon Europe explores how these formal techniques can be deployed and provides real-world examples.

October 26, 2020

One roadblock to the integration of IP from multiple vendors into an SoC is the likelihood of finding duplicate cell names in the merged design. Carefully considered renaming strategies can fix the problem without causing design database bloat.

May 29, 2020

The promise of autonomous vehicles is driving profound changes in the design and testing of automotive ICs.

April 26, 2019

Portable Stimulus allows reuse along horizontal, vertical and technique axes, but you need to be aware of the strengths and weaknesses of each to get the greatest benefits.

March 26, 2019

The computational and algorithmic demands made by computer vision systems highlight HLS' value for AI system development.

March 15, 2019

Bob Smith of the ESD Alliance describes how we can promote the ongoing evolution of the design ecosystem.

March 1, 2019

Application-specific processors can provide high performance for specialised tasks at low energy cost.

October 16, 2018

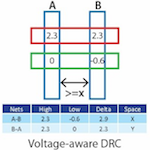

How you can use the dedicated rule decks now being provided by foundries as the foundation for a reliability verification flow.

August 13, 2018

Dina Medhat describes what you need to know about the types of waiver strategy that can be applied.