Better management of timing closure and optimization

How Marvell used an enhanced ECO tool flow for SoC design to cut overall time-to-timing-closure by nearly 70%.

The challenge with timing closure lies, so to speak, in achieving it in a timely manner. If you do not, you will bring a design to market that performs at a lower level than desired, and sales will not meet projections. We have found the task can be efficiently and effectively managed by using an ECO tool in both the timing optimization and closure flows.

This article discusses Marvell’s experience using the TimingExplorer ECO tool from ICScape. We tape out several complex, leading-edge SoCs a year. Timing optimization and closure take up a large amount of our schedules and resources, and they can often involve manual scripting.

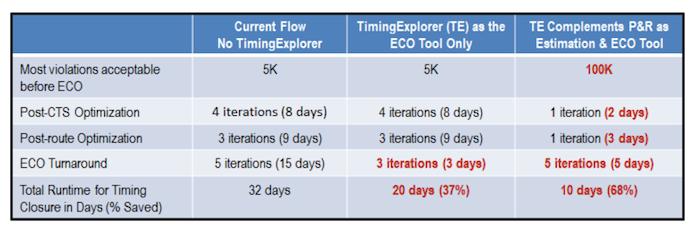

Our experiences around the flow using TimingExplorer in two recently introduced flows are summarized in Figure 1. The headline numbers are that adding the tool to the ECO stage only (i.e., as an ECO tool only) reduced ECO turnaround by 80% and the overall time to closure by 33%. Using it In both the P&R and ECO stages (as Estimation and ECO tool), eliminated several P&R iterations and reduced total time to closure by 68%.

Figure 1 lists runtimes only. It does not include the time that a designer needs to interpret violations and develop an appropriate action plan. That varies from designer to designer since it is a function of his/her design and tool experience. Additional designer-dependent time does play a major role in first two flows, especially at the P&R stage. But extending the tools to the P&R process practically eliminates the time spent by a user on handling those violations also.

Current timing closure and optimization flow

The impact of physical effects on timing is huge. Hence, a design’s final performance cannot be determined until all these effects have been analyzed. In other words, the timing optimization and closure task spans both the design and implementation teams. It can be broken down as follows:

- The design team creates a design and defines its timing parameters.

- The implementation team implements the design to meet the target timing.

- The design team verifies and validates the implementation for “timing” .

An experienced static timing analysis (STA) engineer is typically responsible for verifying and validating the implementation of a design from a timing point of view.

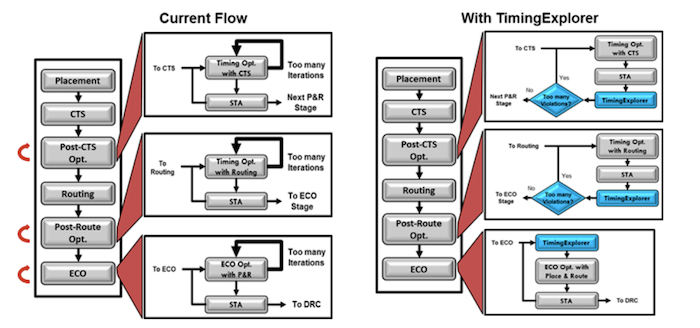

The traditional timing optimization and closure flow (Figure 2) is a two-stage flow. Optimization is primarily done using P&R tools, ECO tools are used to come up with fixes for the remaining violations and these implemented using P&R.

At Marvell, the final 500 or so violations have until now been fixed interactively using a home-grown Perl script-based ECO solution that complements the tools in the ECO flow. The two-stage flow, including drawbacks, is:

1. P&R timing optimization in post-clock tree synthesis and post-route stages

- At each stage in the P&R flow, a designer iterates until the violation count is reduced to a manageable number (c 5,000). This takes time and many iterations.

- A lack of timing and layout correlation between P&R and STA leads to more iterations.

2. STA-based ECO solution

- This is setup aware and supports multi-scenario fixing.

- A lack of physical information leads to inaccurate fixes and long runtimes.

- The last 500 or more violations have to be fixed using a Perl script-based solution that involves manual STA checking

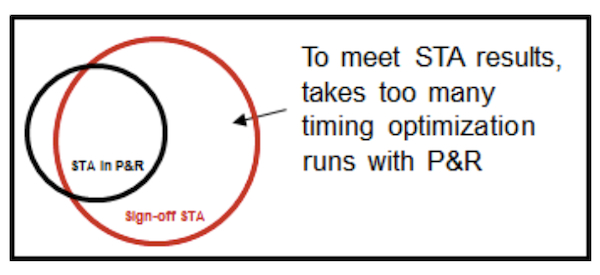

The lack of timing correlation between the signoff STA and the built-in STA engine in a P&R tool leads to a large difference in their respective coverage of timing checks as shown in Figure 3. Then, the lack of layout correlation between the signoff STA and P&R tools leads to inaccurate ECO fixes. If you now add the fact that P&R tools are poor at handling multi-mode, multi-corner (MMMC) timing scenarios, the result is that too many timing optimizations end up being run by the P&R tool.

The new methodology

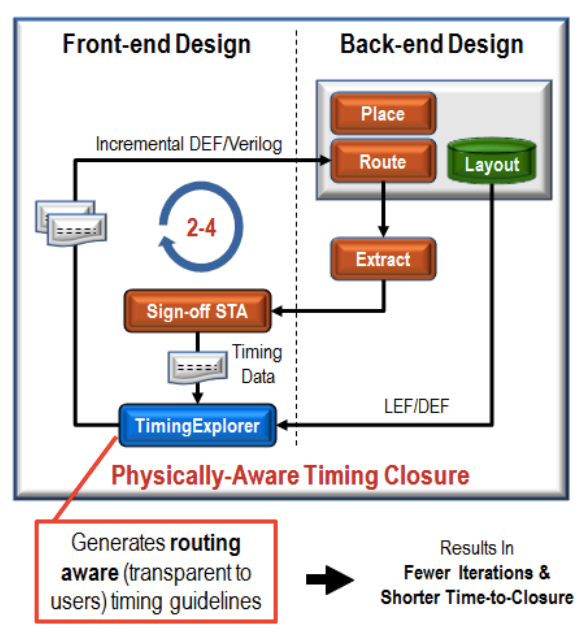

TimingExplorer, when used as the ECO tool reduced ECO turnaround by 37% (Figure 1, Column 3) thanks to fewer iterations. TimingExplorer, (Figure 4) uses sign-off STA data within the built-in physically (P&R) aware optimization engine to analyze and fix timing violations. Unlike a P&R tool, which is focused on the entire design during optimization, TimingExplorer does violation-focused optimization. Hence, it was capable, during our use, of fixing approximately 20X more violations (100K versus 5K for current P&R-based ECO fixing) than an ECO tool. In addition, we found TimingExplorer to be accurate, fast, and predictable.

We decided to see if we could further reduce time to closure by running TimingExplorer in parallel with P&R (Figure 5). Here, we used its predictive analysis capabilities to determine how many of the violations identified by the current P&R run could actually be fixed at the ECO stage. Our designers were able to determine whether to continue iterating using P&R or to move to the next stage and leave the remaining violations to be fixed by TimingExplorer at the ECO stage. This eliminated several long P&R iterations and gave the 68% final reduction in total time to closure. As shown in Figure 5, TimingExplorer analysis runs were performed at post-CTS and post-route optimization stages.

Physical design engineers working together with the STA engineer to close timing were already trained to use TimingExplorer. TimingExplorer’s analysis output is familiar to a typical STA engineer and hence learning to use it was not a problem. However, since timing closure as a problem is not a simple one, and is very design dependent, it takes some effort to master the tool to maximize its value to the problem on hand.

TimingExplorer complementary use has improved our main flow with the following benefits:

- It provides an automated ECO solution that dramatically reduces tape-out stress on the engineers.

- It eliminates P&R iterations and shortens total time to closure by almost 70%.

About the author

Timothy Ying has been working as an ASIC design engineer for 12 years. In his current position as Staff Design Engineer at Marvell’s Storage Group, he is focused on timing ECO closure using Static Timing Analysis. He primarily works on 28nm designs with complex clock structures, multi-voltage domains and hierarchy. Timothy holds a bachelor’s degree in Computer Science from Fudan University in Shanghai, China, and a master’s degree in Electrical Engineering from San Jose State University in California.