Team UVM and emulation for testbench acceleration

Traditional simulation offers greater modeling flexibility and functionality at the IP and block level but takes too long in isolation. Emulation delivers enormous performance gains at the chip, sub-system, and full system levels. You can now get the best of both techniques in a single, unified testbench environment that is reusable and moves with you from the block to the system level, from simulation to emulation.

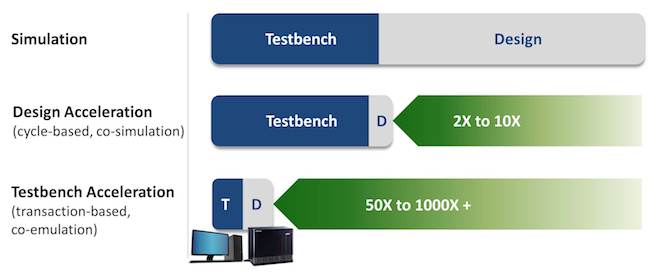

Whether you call it testbench acceleration, simulation acceleration, or co-emulation, this targeted emulation use-case offers interoperability, flexibility and performance. It lets the RTL design-under-test running in a hardware emulator interact with a testbench running on a workstation. Using a hardware emulator to accelerate simulation can be especially effective when the transactors are emulation-ready, running at 1000X the speed of simulation alone (Figure 1).

Figure 1. Using emulation with simulation accelerates performance for dramatic testbench acceleration (Mentor Graphics)

The benefits of adopting hardware-accelerated simulation include:

- Increased performance and productivity during verification;

- Vertical reuse through platform portability;

- Reduced development effort; and

- Substantially lower risk at design tape-out.

Practical testbench acceleration

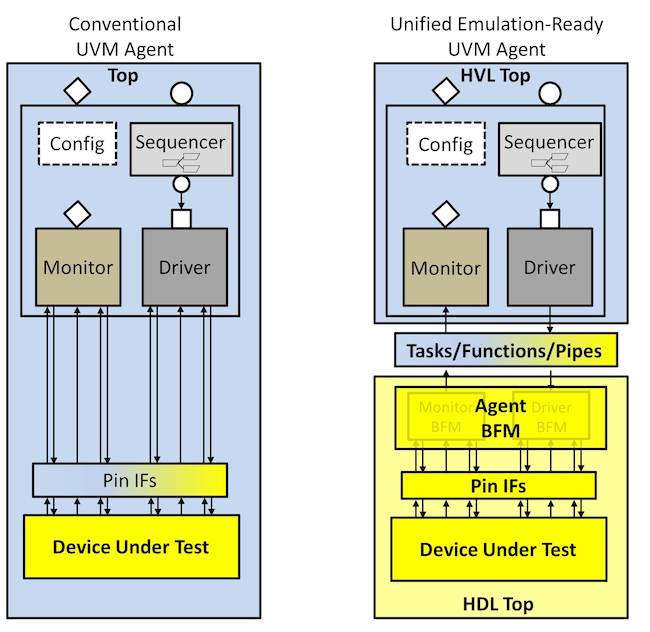

Transaction-based communication is key. Transaction-based testbench acceleration using emulation requires two separate hierarchies—one synthesizable, the other untimed—that transact together without direct cross-hierarchy signal accesses. Creating a unified testbench flow for both simulation and emulation takes only three steps:

- Employ two separate domains: an untimed hardware verification language (HVL) domain and a synthesizable hardware description language (HDL) domain.

- Model all timed testbench code for emulator synthesis in the HDL domain, leaving the HVL domain untimed.

- Devise a transaction-level, function call-based communication API between the HVL and HDL domains.

While the concepts are straightforward, you should plan emulation as soon as you start testbench development to avoid creating extra work for yourself and your team. Creating emulation-ready testbenches entails careful architectural consideration, but the performance benefits can be substantial.

For example, Figure 2 illustrates the difference between a conventional UVM agent and a unified emulation-ready UVM agent. The testbench view remains the same; the structure underneath is different but is still transparent to the UVM testbench layers. This revised emulation-ready testbench architecture offers maximum leverage of existing verification techniques and capabilities.

The extent of the testbench acceleration depends on several factors. For example, the efficiency and quality of the testbench, function calls and data transfer to and from the HDL domain are fundamental to achieving optimal performance. Best practices should also be learned and adopted to reduce the hardware-software communication overhead and increase emulator throughput to improve the runtime.

More on testbench acceleration

For those of you who want to exploit these efficiencies, Mentor Graphics recently published a series of three whitepapers. They introduce the fundamental concepts and present the architectural and modeling requirements for SystemVerilog and UVM testbench acceleration using hardware emulation, as well as the steps to achieve optimal acceleration speed-up.

Now online, you can access them at the following links:

- Reducing Design Risk with Testbench Acceleration

- Testbench Acceleration Performance Demystified

- Optimizing Testbench Acceleration Performance

About the author

Dr. Hans van der Schoot is a recognized specialist in verification technology and works as a methodologist in the Emulation Division at Mentor Graphics. Hans has a solid background and wealth of knowledge in functional verification from many years as a researcher, engineer and consultant, with extensive practical experience providing verification methodology and implementation consulting and training services. He has authored multiple papers pertinent to hardware verification and software testing.

Hans obtained his doctorate degree in computer science from the University of Ottawa, Canada, after graduating from the University of Twente in the Netherlands, also in computer science.

Hans van der Schoot is a methodologist in the Emulation division of Mentor Graphics

Hans van der Schoot is a methodologist in the Emulation division of Mentor Graphics