3D-IC integration – a stepwise approach

2.5D-IC integration overcomes 2D limitations such as cost, offchip bandwidth bottlenecks and I/O pin scarcity, and offers a route to true 3D-IC integration.

There are three good reasons to start considering three-dimensional (3D) integration technologies as a serious option for your IC designs today.

The first is that two-dimensional (2D-IC) integration is becoming more expensive. A 100mm2 die made using a 20nm foundry process featuring FinFET transistors and double-patterning lithography may cost up to 70 per cent more than the same die made using a 28nm high-k metal gate foundry process. Future integration decisions will be made on the basis of what is affordable, rather than what is possible, especially as although digital logic shrinks with each process node, analog blocks tend not to.

The second reason to consider 3D-IC integration technologies is off-chip bandwidth. Over the last several years, the number of processor cores per chip has doubled every two years, while the number of package pins has remained about the same. In order to feed the cores at the required data rate, SerDes I/Os are being used, whose speed has doubled only every four years. The number of SerDes I/Os per chip, in turn, has only marginally increased, due to their size. As a consequence, the total throughput per chip has increased much slower than it would be required.

Take a recent design by Oracle, its SPARC-based T3 processor; this chip achieves a 2.4Tbit/s aggregate bandwidth using SerDes I/Os that occupy about 60mm2, or 15 per cent of the die area, and consume about 30W, or 22 per cent of its power consumption. A 20Tbit/s bandwidth, if implemented using today’s state-of-the-art 28Gbit/s SerDes I/Os, made on a 28nm foundry process, would require about 200mm2 of silicon area, and would consume more than 200W.

Using 3D-IC integration technologies to achieve greater functional integration, or to explore other forms of I/O such as optical connections on separate die, would reduce the need for ‘off-chip’ bandwidth.

The third reason for considering 3DIC techniques is to overcome the I/O pin limitations created by increasing functional integration on-chip. Although Moore’s Law has enabled us to put more transistors, and therefore more functionality, on a die, it hasn’t radically altered the number of I/O pins we can squeeze into the same area. FPGA maker Xilinx, for example, found that the number of I/O pins per thousand logic cells in its largest FPGA at a given technology node, has decreased thirtyfold during the progression from 180nm to 45/40nm processes. Data for the 32/28nm node are not available, since Xilinx started using 2.5D-IC integration at this node.

Evolving from 2D- to 3D-IC integration

2D integration on planar ICs is becoming more challenging, as we can see in the rising cost of silicon area at advanced process nodes. Full 3D-IC techniques, where bare die are stacked one on top of another and interconnected with through-silicon vias (TSVs), offers powerful integration opportunities but the ecosystem to support the technique is still evolving.

One way to get many of the benefits of 3D integration is to use 2.5D-IC techniques, based on the use of a silicon interposer. One advantage of the 2.5D-IC approach is that a silicon interposer can achieve very fine interconnect features, as compared to both package substrates and TSVs. This means they will play a role in integration strategies until the pitch of TSVs – today 40 microns – approaches the pitch of global wiring pitch – 0.8 microns at 28nm – making the cost of horizontal and vertical connections more comparable. The aspect ratio of TSVs will also have to improve from today’s 10:1, which will make it easier (and therefore less costly) to handle thinned wafers.

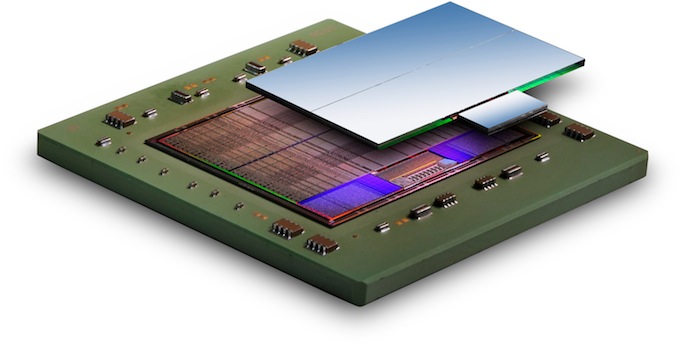

Xilinx demonstrated the viability of the silicon interposer in 2010 by using the approach to interconnect several FPGA die. It has since moved to a heterogenous approach, adding SerDes I/O die alongside the FPGAs. Both were built using TSMC’s Chip on Wafer on Substrate (CoWoS) technology.

Figure 1 Xilinx has demonstrated the value of heterogenous 2.5D-IC integration in its latest FPGAs (Source: Xilinx)

The ecosystem is now in place and equipment manufacturers, silicon foundries, OSAT, and EDA companies have demonstrated the full technical feasibility of more than 2D-IC integration. Throughout 2013, we will see more announcements of 2.5D-IC products, a sign of growing confidence in the potential of more than 2.5D-IC integration.

True 3D-IC technology is also progressing, but is not yet ready for mass adoption. For example, in spite of very promising results, 3D-IC integration of Wide I/O memory and application processors for mobile applications has been postponed due to significant improvements in standard DDR memory, which have made it possible to deliver the desired bandwidth using more traditional 2D-IC integration.

3D-IC integration design flows

Synopsys has been able to adapt its advanced physical implementation, RC extraction, DRC/LVS, static-timing analysis, design-for-test and Spice simulation tools to support 2.5D-IC and 3D-IC design. During this process, we haven’t found any technical roadblocks to applying these 3D integration techniques, and so the enhanced tools are now available.

For example, in physical implementation, we have complemented our Manhattan router, which is used to route the silicon interposer interconnect, with a 45-degree-capable router to handle the dense redistribution layers. In Spice simulation, we have expanded the capabilities of both the modeling language and the simulation engine to enable the co-simulation of different modules using different models and operating conditions.

Synopsys is also working with engineering teams that want to use 2.5D- and 3D-IC technologies. For example, to help accelerate the design of heterogeneous 3D-IC systems using silicon interposers with TSVs (also known as TSIs), we are collaborating with A*STAR Institute of Microelectronics of Singapore and have joined the TSI Consortium. Together we’ll demonstrate a design and manufacturing flow, and optimize TSI technology for both cost-and performance-driven applications.

There are other opportunities to extend traditional EDA tools to support 3D integration. For example, virtual and fast prototyping are ideal for highly heterogeneous systems such as 3D-IC; thermo-electro-mechanical simulation is also critical, and TCAD – while originally meant for process technology development – is an extremely powerful technology for modeling the thermo-electro-mechanical effects introduced by 3D structures.

More than Moore

Xilinx has already demonstrated the value of heterogenous integration on silicon interposers, using different, optimised manufacturing processes to make its core logic and fast I/O chips. 3D integration techniques will enable the industry to take this idea a stage further to integrate other forms of device, such as optical transceivers or even micro-electro-mechanical systems (MEMS), such as multi-axis accelerometers, compasses, gyroscopes, microphones, and pressure sensors.

In smartphones and tablets, it is becoming common to see the application processor surrounded by MEMS on the same printed circuit board. In future this may evolve to a 2.5D-IC integration, and finally to a full 3D-IC implementation in which the functionality is repartitioned among the various die for greater efficiency. Silicon photonics may enable the continued increase of continued performance scalability of “more of Moore” systems, as well as to spark the transition to a new generation of “more than Moore” systems, and is ideally suited for both 2.5D-IC and 3D-IC integration. There are many great opportunities to extend the breadth of EDA solutions to accelerate these innovative technologies.

Conclusions

The technology to implement 2.5D-IC has already been proven in use by companies such as Xilinx. Enabling the wider uptake of 3D integration techniques, and especially of 3D-IC integration, will rely on the willingness of all parties in the ecosystem to work together, sometimes sharing the burden of debugging existing features, testing them, and accepting temporary workarounds while waiting for a new feature to become available. No technology is perfect at launch, but current progress suggests that 3D integration techniques have changed from being a technology of the future to being a technology for the present.

Steve Smith, senior director, 3D-IC marketing and strategy, Synopsys

Author

Steve Smith is responsible for Synopsys’ 3D-IC strategy and marketing. He has been with Synopsys for 15 years, having served in various functional verification and design-implementation marketing roles. He has worked in the EDA and computer industries for more than 30 years in senior positions including marketing, applications engineering, and software development. Prior to Synopsys, Steve worked at Viewlogic, CrossCheck, Teradyne, Unisys, and ICL.

Steve holds a bachelor’s degree in statistics and numerical analysis from Lancaster University, England.