Why cell-aware testing is important

The goal of silicon testing is to find defective parts before they are shipped to the customer. We measure our success (or failure) to do this in defects-per-million (DPM), and the lower the number, the better the reliability. The usual methods involve adding scan-test structures to the design, then applying fault models to pattern-generation tools that represent issues such as stuck-at and transition defects. This provides high defect detection, but mostly for faults at the gate (or cell) boundary, or between library cells. However, today’s fault models like stuck-at, transition- and path-delay are no longer sufficient for detecting all faults and especially defects within cells. With more recent fabrication technologies, the number of defects occurring within cells is significant, perhaps amounting to roughly half of all defects [1]. Thus, it is important to ensure that you properly define fault models that target these ‘cell-internal’ or ‘cell-aware’ defects.

Test professionals can now use the physical design of cells as a way of understanding how to target the cell-internal defects. This involves performing a library characterization to determine where defects can occur and how they affect the operation of each cell.

You might ask why cell-aware ATPG is so necessary for finding defects that stuck-at and transition patterns presumably miss. That is a logical and valid question since production test based on stuck-at and transition has worked for many years. Modern integrated circuits increasingly use highly complex cells, some with high drive strengths, which mean more internal components such as transistors and resistors. It is no longer rare to find library cells with several hundred parasitic resistors and coupling capacitors, which means there could be hundreds or thousands of locations for defects in a cell. Neighboring interconnect lines also have to be taken into account as potential sources of resistive bridge defects or shorts, and narrow lines can become open defects.

Without dedicated cell-aware ATPG, it is difficult to achieve the required low defect rates on designs using these complex cells whose defects cannot be addressed sufficiently with traditional inter-cell oriented fault models – thus the need for test patterns for possible cell-internal defects.

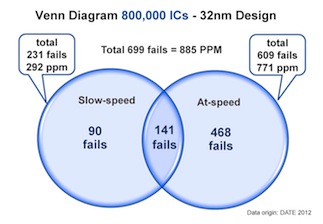

The first published industrial results of using a cell-aware testing strategy [2] showed large reductions in defect density. Later reports have shown an 885 DPM improvement with cell-aware testing, as shown in Figure 1, an important result for many production environments [3]. Recent validation of these results through system-level-test has shown that cell-aware detected defects are uniquely detecting cell-internal defects.

Figure 1

Improving PPM (Source: Mentor Graphics – click image to enlarge)

In a nutshell – cell-aware testing will be very important for future integrated circuits. It is easy to apply (you only need to characterize a library cell once for a certain process technology), it will not break your current test flow, and it will add several percent to your defect coverage.

So the question is: why not use cell-aware test now?

References

- F.Hapke, W.Redemund, J.Schloeffel, R.Krenz-Baath, A.Glowatz, M.Wittke, H.Hashempour, S.Eichenberger, “Defect -Oriented Cell-Internal Testing”, International Test Conference (ITC10), Austin, TX, USA, October 2010

- F. Hapke, J. Schloeffel, W. Redemund, A. Glowatz, J. Rajski, M. Reese, J. Rearick, J. Rivers, ”Cell-aware Analysis for Small-delay Effects and Production Test Results from Different Fault Models”, International Test Conference (ITC11), Anaheim, CA, USA, September 2011

- F.Hapke, J.Rivers “Cell-aware library characterization for advanced technology nodes and production test results from a 32nm processor”, Design Automation an Test Conference Europe (DATE’12), Dresden, Germany, March 2012

Author

Juergen Schloeffel is a product and governmental relations manager in the area of EDA and DFT at Mentor Graphics Development in Hamburg, Germany. His current interests include advanced testing techniques, failure diagnosis, design automation for DSM technologies and 3D test. He holds several patents and is author and co-author of more than 50 conference papers and journals. Juergen received a diploma degree in physics from Georg-August-University in Goettingen, Germany. He can be reached at juergen_schloeffel@mentor.com.

Juergen Schloeffel is product and governmental relations manager in the area of EDA and DFT at Mentor Graphics in Hamburg, Germany. His current interests include advanced testing techniques, failure diagnosis, design automation for DSM technologies and 3D test.

Juergen Schloeffel is product and governmental relations manager in the area of EDA and DFT at Mentor Graphics in Hamburg, Germany. His current interests include advanced testing techniques, failure diagnosis, design automation for DSM technologies and 3D test.