Improving SoC productivity through automatic design rule waiver processing for legacy IP

You can waive some physical verification errors related to legacy IP found in foundry DRC checks. Knowing which has involved lengthy manual analysis. TSMC is enhancing the process with automation.

New or expanded design rules are introduced at each new node. However, larger system-on-chip (SoC) designs often incorporate a significant (and growing) amount of custom and third-party legacy intellectual property (IP).

This IP may have been designed during different versions of the target foundry’s design rule manual, or for slightly different processes. The resulting differences frequently result in DRC errors against the current design rules.

Some physical verification (PV) errors associated with known IP blocks can be waived at the foundry’s discretion. The problem is that waiver management has historically been a manual, time-intensive process. New automated techniques improve waiver accuracy and reduce processing time.

Traditional waiver management

Traditional waiver strategies require manual rule deck modification, with no guarantee that these modifications will not reduce the deck’s integrity at final signoff.

The modification normally involves the use of a marker layer to waive the violations that interact with a design layer. However this approach is susceptible to human error, and there is a significant risk that some real errors will be inadvertently waived.

First-generation EDA waiver systems (many still in use) rely on manual recording of waiver information, followed by a post-processing step to remove the errors, based on matching existing errors to the waiver data. Such matching is based on exact detailed matching, with error results identified and then waived only if found from the exact same cell.

Unfortunately, with context-dependent design rules, some errors may be modified in shape, or promoted out of the cell when a piece of IP is placed into context. This makes them impossible to waive using historic approaches. Where such errors are not waived properly, the designer has to manually (and unnecessarily) review the results.

Additionally, when an IP block with waivers is passed to another team for incorporation into a design, the waiver information is transferred neither in a consistent manner nor in a format that allows for easy identification of the waived errors during PV of the integrated design.

The lack of standardization and automation for IP waiver processing typically leads to waived errors reappearing at the full-chip level, without any indication of their waived status.

For today’s advanced nodes, SoC-level verification engineers are too often forced to wade through tens of thousands of false errors. This wastes valuable human effort and delays product delivery. Determining which errors should or should not be waived is both very difficult and very time-consuming, requiring extensive communications between IP designers and foundry partners.

Automated IP waiver management

In the last two years, highly sophisticated automated waiver management processes have been introduced by the EDA industry. For example, the Calibre Automatic Waivers system addresses the issues we have discussed by pushing the waivers into the PV run itself. It automatically recognizes and removes previously waived design rule violations in IP, eliminating redundant error debugging while ensuring that all waived errors are properly identified during the full-chip verification run.

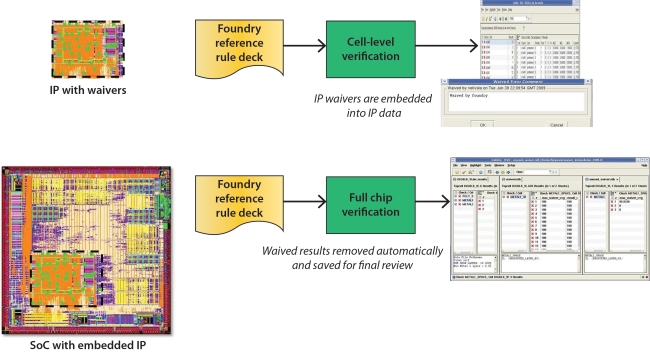

The generation of waivers is best handled by the IP provider when debugging PV results for the IP cell or block in question. While debugging results with a graphical debugging tool (e.g., Calibre RVE), users can highlight the results in a layout viewer. In our example, using the expanded capabilities of Calibre RVE, the user can then mark a selected result as ‘waived’, as shown in Figure 1.

The waived results are automatically exported to a database in GDSII or OASIS, the industry-standard layout formats, and this is delivered together with the IP. In PV runs on the full design, Calibre nmDRC with Automatic Waivers can identify these waiver shapes and compare them to results for the same rules in context. Upon completion of the Calibre DRC run, the waived errors are removed from the error list and reported separately.

Figure 1 Automated waiver processing (Source: Mentor Graphics/TSMC)

Unlike traditional waiver strategies and older semi-automated waiver processing, a fully automated flow ensures that any results that were promoted out of the original IP can still be accurately identified and removed.

Also, with the addition of user-specified tolerances, results can be waived even when the result shapes do not exactly match the originally waived error from IP.

Finally, all results that are waived during this process are saved and stored in a separate database for final review. This allows the designer to confirm that there are no masked results for errors that do require design modification.

All of this processing is done without requiring any modifications to the user’s foundry reference PV rule files.

Automated waiver adoption by TSMC

Communicating waivers between the design and foundry teams can be a big time sink. Given that, it is also easy to inadvertently lose information in the process accordingly.

TSMC recognized the needs to incorporate waiver information directly into IP datasets, and to make it available wherever the IP is used.

Doing so helps both TSMC and its customers. For customers, it cuts debug time wasted reviewing waived DRC violations. For the TSMC team, it gives them immediate visibility into exactly which results were waived for a given rule. This approach also greatly expedites communication and the resolution of any problems.

TSMC is supporting appropriate CAD layers for automated waiver processing in its 28nm process. It makes them available to IP designers using a standard layout editor environment through appropriate foundry process design kit (PDK) support. This ensures that some other tool does not inadvertently generate data on the layers reserved for automated waiver data, or vice versa.

In addition, TSMC is implementing automated waivers (e.g., including Calibre Automatic Waivers within TSMC I/O libraries) for customers who are taping out to TSMC using a Calibre DRC rule file.

TSMC’s adoption of an automated waiving solution for its own IP is already speeding up the verification of large SoCs and reducing PV debugging time.

It is eliminating unnecessary communication loops between designers and TSMC about previously waived IP. It is improving the accuracy of the error waiving process. And ultimately, it is reducing time-to-tapeout and delivering better products.

About the authors

Nermeen Hossam is the DRC Engineering Lead for the Calibre Marketing Group at Mentor Graphics in Cairo, Egypt.

John Ferguson is the Director of Marketing for Calibre DRC Applications at Mentor Graphics in Wilsonville, Oregon.

Anderson Chiu is the Marketing Manager for Design Methodology and Service Marketing at TSMC.

Chien-Ming Chiang is a Senior Engineer in the I/O Library Department of TSMC.

Contact

Mentor Graphics

Corporate Office

8005 SW Boeckman Rd

Wilsonville

OR 97070

USA

T: +1 800 547 3000

W: www.mentor.com

TSMC

25 Li-Hsin Rd

Hsinchu Science Park

Hsin-Chu

Taiwan 300-78

R.O.C.

T: +886 3 563 6688

W: www.tsmc.com