signal integrity

Overcoming increasing PCB complexity with automation

Designing a PCB for power integrity

Reducing system noise with hardware techniques

Circuit noise problems can originate from a variety of sources. By carefully examining attributes of the offending noise you can identify it’s source, thereby making noise reduction solutions become more apparent. There are three subcategories of noise problems: device, conducted and radiated noise. If an active or passive device is the major noise contributor, you […]

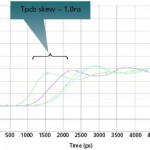

Board-level timing analysis

This paper builds on “Timing Numbers In ICX – What do we do with them?” [1]—a paper presented at the 2006 Mentor Graphics User2User conference (and now available for download at the journal’s Web site, www.edatechforum.com). The original paper focused on the need for timing analysis and the theory behind it; this paper takes a […]

Multi-corner multi-mode signal integrity optimization

Signal integrity (SI) is an ever-growing problem as more interconnect effects and fast clocks increase the chances of crosstalk noise and glitches as well as unexpected signal delays. There has been a significant increase in SI-related timing violations due to the increasing influence of lateral wire capacitance in designs at 65 and 45nm. A fast-increasing […]

PLATINUM SPONSORS

View All Sponsors