October 19, 2023

Standard physical verification (PV) check reviews within EDA tools can reduce time-to-tapeout and mitigate risk.

May 10, 2022

Coordinate-based checking provides a streamlined way to verify designs around ESD before full-chip runs without the need for custom checks.

September 13, 2021

Delivering physical implementations at new process nodes is getting ever harder. Learn how to stay on track by checking work is rule-compliant as you go.

May 31, 2021

Using on-demand rule checks during place-and-route boosts efficiency and design quality.

October 16, 2020

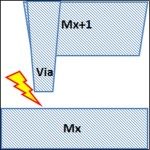

Reliability rule checks need - and now get - more granular analysis that allows designers to adopt proposed waivers with much greater confidence.

September 21, 2020

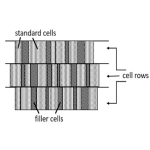

A physical verification-ready flow can speed project delivery by making your use of filler cells more efficient.

August 14, 2020

For physical verification and beyond, each process node requires new thinking, new tools and greater performance.

June 9, 2020

A collaboration between GlobalFoundries and Mentor has resulted in an innovative in-design fixing strategy across markets such as IoT, mobile, RF, graphics and networking.

May 26, 2020

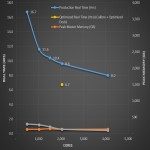

A Mentor-Microsoft-AMD pathfinder demonstrates the potential benefits of cloud-based physical verification.

April 14, 2020

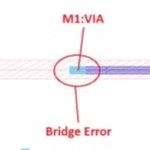

Early detection using design integrity checks during implementation from abstract LEF/DEF inputs can deliver major efficiencies.