March 29, 2024

RISC-V adoption is growing fast as is the ecosystem around the open-source core. Hardware and software are now vital for appropriate debug.

April 9, 2021

The best paper winner at DVCon 2021 details a comprehensive methodology for making the best use of formal verification for bug hunting

April 6, 2021

Joe Sawicki of Siemens EDA recently addressed the main trends in design delivery from architecture to validation to digital twins - and where they may soon take the industry and its products.

August 12, 2020

Learn how an IDE offers on-the-fly, auto-correct and informed analysis of VHDL code to speed project quality and delivery.

February 14, 2020

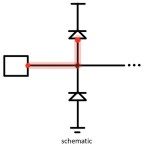

P2P (point-to-point) resistance is fundamental to IC reliability verification. Handle it more efficiently with detailed, automated path layout analysis.

July 23, 2019

An IDE designed to catch typographical errors, missing declarations and inconsistent references in your code can hugely reduce your time in debug.

June 18, 2019

Integrated design environments and features within them such as auto-complete deliver valuable efficiencies for input, verification and debut.

June 11, 2019

How to remove or extract portions of a layout for easier, more focused and faster project delivery.

February 6, 2019

UPF provides a useful way to describe the power-management strategies that should be applied to a design, but using it introduces a number of challenges during low-power debugging.

January 7, 2019

Escape formal's narrower definitions with a flow that shows you how to Avoid, Detect, Erase, Prove Absence and Tape Out while avoiding bugs.