October 6, 2022

3D-IC presents major connectivity challenges in maintaining a golden netlist and managing necessary exceptions. Learn how to manage them.

March 29, 2018

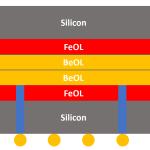

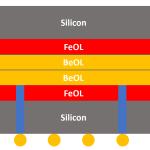

3D integration technology has split into a number of different approaches, each of which brings a different combination of benefits in terms of performance.

September 23, 2015

AMD's Radeon R9 family is the result of eight years developing 3D-IC and interposer technology. What lessons did the company learn?

September 10, 2014

Innovation in physical verification is driven by incoming nodes but new tools and features can and should be fed back up the technology chain.

August 7, 2014

FinFET and 3DIC technologies bring with them not just higher performance but an increased need for accurate parasitic analysis.

June 18, 2014

How to enhance an 'ideal' parastitic extraction strategy to create a full 3D assembly-level parasitic netlist for simulation and circuit analysis.

April 8, 2014

Fighter pilots have long trusted highly sophisticated automation. That’s how you can meet the challenges posed by advanced PCB design techniques.

October 11, 2013

PGA has been IC-centric for mainstream 2D configurations. It must become system-centric for 2.5D and 3D systems.

September 24, 2013

Mobile and networking platforms need high bandwidth, low power consumption, and small footprint. These needs drove standards, such as LPDDR4, Wide I/O 2 and Hybrid Memory Cube.

August 12, 2013

3D-IC design is ready for take-off, following several years of intense collaboration to develop the necessary tools, methodologies and flows